HBM:高带宽内存吸引各大科技巨头抢购的“魔力”到底是什么?

全球第二大存储芯片巨头SK海力士昨天公布了最新财报,截至6月当季销售额约合57亿美元,较上年同期下降47%,超过了6.05万亿韩元的平均预期,相比一季度创纪录的亏损有所收窄。

本文引用地址:http://www.eepw.com.cn/article/202307/449029.htm由于各大企业对布局AI领域的兴趣激增,同时,SK海力士在用于生成式AI领域的高带宽存储器(HBM)DRAM方面处于市场领先地位,其二季度用于AI领域的高性能DRAM销售增长强劲,对高端DRAM的需求增长了一倍多。

继英伟达之后,全球多个科技巨头都在竞购SK海力士的第五代高带宽内存HBM3,包括AMD、微软和亚马逊等等。SK海力士首席财务官Kim Woohyun透露,将继续扩大其高端存储芯片的产量,以满足人工智能驱动的需求。

新一代DRAM解决方案

当代电子计算体系的表现完全依赖于处理器和内存的相互配合,而来到了AI时代,大模型处理数据的吞吐量更是呈指数级增长,最新的GPT-4模型据说有1.76万亿参数量,要想支撑如此庞大的数据处理和传输,对内存就提出了更高的带宽需求。

然而,存储器和处理器并没有同步发展,处理器的性能按照摩尔定律规划的路线不断飙升,对比内存所使用的DRAM从工艺演进中的获益却很少,性能提升速度远慢于处理器速度。据行业预计,处理器的峰值算力每两年增长3.1倍,DRAM的带宽每两年增长1.4倍,相差1.7倍。

当存储器的性能跟不上处理器,对指令和数据搬运(写入和读出)的时间将是处理器运算所消耗时间的几十倍乃至几百倍。数据交换通路窄以及其引发的高能耗,导致DRAM的性能成为制约计算机性能的一个重要瓶颈,即所谓的“内存墙”。

HBM突破了内存容量与带宽瓶颈,打破了“内存墙”对算力提升的桎梏,被视为新一代DRAM解决方案,是未来DRAM重要发展路径。这种新型的内存方案具备高带宽、低功耗的特点,已逐渐在竞争中脱颖而出,面对AI大模型这种动不动千亿、万亿的参数,服务器中负责计算的GPU几乎必须搭载HBM。

什么是HBM

HBM(High Bandwidth Memory,高带宽存储器),与其他DRAM最大的差别就是拥有超高的带宽,目前最新的HBM3的带宽最高可以达到819GB/s。HBM为何能拥有如此大的带宽?

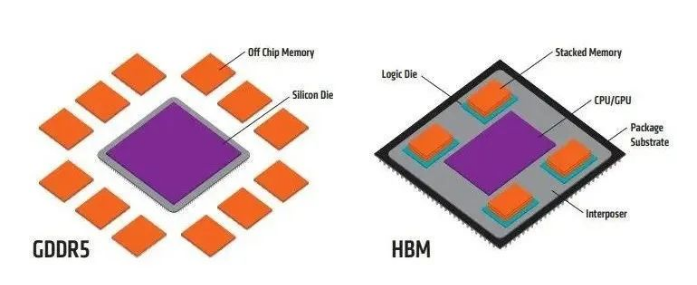

那么就要从HBM的原始形态GDDR说起,GDDR采用传统的方法将标准PCB和测试的DRAMs与SoC连接在一起,是将DRAM芯片直接放置在PCB上并围着处理器转一圈的独立封装。因此会受到来自PCB面积的约束,互联线长/带宽以及通讯延迟也会随之增大。

相对于传统内存,HBM则是在硅中阶层(Silicon Interposer)上堆叠起来并和GPU封装在一起,这样一来,面积一下子缩小了很多,并且HBM离GPU更近了,数据传输也就更快了。

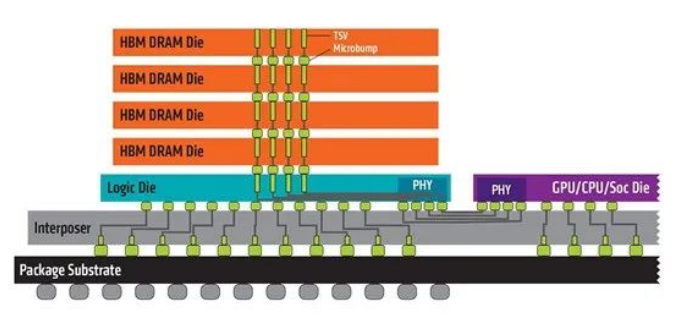

HBM之所以可以做到这样的布局,是因为采用了3D堆叠技术,将DRAM裸片垂直叠放在一起,这相当于在一样的“占地面积”下能布置比过去多数倍的DRAM颗粒。这种堆叠方式不仅节约空间,而且能够带来更短的颗粒间距进而缩短信号传输路径及延迟,但HBM真正的难点在于这些颗粒的互联问题,直到有了TSV技术之后才得以解决。

硅通孔技术(Through Silicon Via, 简称“TSV”)将“每层楼”连接在一起,是连接硅晶圆两面并与硅衬底和其他通孔绝缘的电互连结构:在保证强度以及完整性的前提下在芯片(硅)上垂直穿孔,然后以这些孔为通路进行布线并完成垂直互联。贯通所有芯片层的柱状通道传输信号、指令、电流,以增加吞吐量并克服单一封装内带宽的限制。

凭借TSV技术,HBM大幅提高了容量和数据传输速率,与传统内存技术相比,HBM具有更高带宽、更多I/O数量、更低功耗、更小尺寸,可应用于高性能计算(HPC)、超级计算机、大型数据中心、AI、云计算等领域。随着5G商用到来,存储数据量激增,市场对于HBM的需求将有望大幅提升。

存储巨头争霸HBM

在DRAM的整体颓势之中,HBM却在逆市增长,自从去年ChatGPT出现以来,HBM作为AI服务器的“标配”,更是开始狠刷存在感。超高的带宽让HBM成为了高性能GPU的核心组件,目前,高端GPU市场被英伟达和AMD瓜分,最新的H100和MI300X都配备了目前最新的HBM3。

预测到2031年,全球高带宽存储器市场预计将从2022年的2.93亿美元增长到34.34亿美元,在2023-2031年的预测期内复合年增长率为31.3%。当前HBM市场呈现三足鼎立格局,TrendForce研究显示,2022年三大原厂HBM市占率分别为SK海力士占50%、三星约40%、美光约占10%。

SK海力士

SK海力士早在2021年10月就发布了全球首款HBM3,并于2022年6月正式量产,是目前唯一能量产HBM3产品的供应商。

SK海力士HBM技术起步早,从2013年与AMD联合开发了全球首款HBM后,第一个站上HBM的跑道后就一直是HBM行业的领头羊,得益于自主研发的MR-MUF(Mass Reflow Molded Underfill)技术,目前占据全球HBM市场一半以上的市场份额。

2023年4月,SK海力士宣布已在全球首次实现垂直堆叠12层硅通孔技术垂直堆叠的芯片,实现最高容量24GB,容量较上一代HBM3 DRAM提升50%,还搭载了ECC校检(On Die-ErrorCorrection Code),可以自动更正DRAM单元(cell)传输数据的错误,从而提升了产品的可靠性。

此外,SK海力士预计在今年年底前供应HBM3E样品,并在2024年开始量产,将下一代产品HBM4的生产目标时间定在了2026年。

三星跳过HBM1,于2016年首次量产HBM2产品,同一年发布了4GB和8GB的HBM2 DRAM;2020年2月,三星正式宣布推出其16GB HBM2E产品“Flashbolt”。

2021年三星宣布了一项新的突破,面向AI人工智能市场首次推出了HBM-PIM技术,在存储芯片上集成了计算功能而不是CPU、内存数据分离,实现了原HBM2两倍的性能,同时功耗还降低了70%。预计2024年实现接口速度高达7.2Gbps的HBM3P,2025年在新一代面向AI的GPU中见到HBM3P的应用。

美光最开始是和英特尔一起开发HMC(混合内存)技术,虽然也使用了TSV,但是和HBM完全不同,也不兼容。直到2018年美光才正式放弃HMC,开始追赶HBM,于2020年7月宣布大规模量产HBM2E,HBM3也仍作为其产品线在持续研发之中,预计将于2024年初开始量产。

HBM的下游也在持续发力,英伟达历代主流训练芯片基本都配置HBM;英特尔Sapphire Rapids发布全球首款配备HBM的X86 CPU;AMD也在持续更新HBM产品线。

同时值得一提的是,由于HBM主要和GPU搭载使用,封装主要以TSV 3D封装进行,所以通常在晶圆厂内完成,当前台积电、格芯等也在发力HBM技术的研究与制造。

台积电宣布与博通合作强化CoWoS平台,该平台技术常用于HBM的整合封装,新一代CoWoS技术能够容纳多个逻辑系统单芯片以及多个HBM。业内消息称台积电将量产其第六代CoWoS技术,可在单个封装内集成12颗HBM。

格芯与SiFive也宣布共同开发基于12LP/12LP+ FinFET工艺的HBM2E。据介绍,SiFive基于格芯12LP平台和12LP+解决方案的可定制HBM接口将实现高带宽存储轻松集成到单个片上系统(SoC)解决方案中。

存储巨头相继入局、上下游厂商发力,HBM受到越来越多的关注与青睐,有人甚至认为HBM未来将取代DDR。

VR和AR是HBM未来将主要发力的领域。因为VR和AR系统需要高分辨率的显示器,这些显示器需要更多的带宽来在GPU和内存之间传输数据。而且,VR和AR也需要实时处理大量数据,这都需要HBM的超强带宽来助力。苹果最新推出的头显设备Vision Pro也传出内置了SK海力士专门设计的高带宽DRAM来提升图像数据的处理效率。

此外,智能手机、平板电脑、游戏机和可穿戴设备的需求在不断增长,这些设备需要更先进的内存解决方案来支持其不断增长的计算需求,HBM也有望在这些领域得到增长。并且,5G和物联网(IoT)等新技术的出现也进一步推动了对HBM的需求。

在自动驾驶方面,智能汽车和车路协同场景都涉及大量的数据传输,HBM的带宽优势能够发挥作用,但是由于成本问题,HBM3距离“上车”还有些时日。

目前而言,DDR仍为DRAM市场主流产品,与庞大的DRAM市场比起来,HBM市场占比较低,大约只占整个DRAM市场的1.5%。现在HBM还是主要应用于服务器、数据中心等领域,消费领域对成本比较敏感,因此HBM的使用较少。亦仍有待进一步提升技术、降低成本,HBM未来或将大有所为。

新技术革新的难点

目前困扰HBM的问题之一是成本,3D堆叠成本高昂。因为有一个逻辑芯片位于芯片堆叠的底部,这是必须支付的额外硅片,然后是硅中介层,最后还需要一个更大的封装等等,这是需要付出昂贵代价的。

同时,由于HBM采用复杂的TSV封装工艺,其生产良率较低,产品开发周期较长,生产成本也较高。并且如果组成垂直结构的一部分完全失效,则必须丢弃整个结构,这会使通过TSV互连的系统制造起来更加昂贵。目前存在的HBM脱离了消费者领域,相比之下GDDR6等图形内存虽然无法提供与HBM一样多的性能,但成本却显著降低。

另外,芯片在某些温度条件下达到其时钟速度,如果附近有另一个也会发热的芯片会受到影响。大量DRAM堆叠和GPU封装在一起产生大量的热,如何散热也是HBM极大的挑战。

虽然HBM的高带宽小体积是优点,但是其堆叠工艺导致它缺乏灵活性,导致难以扩容且访问延迟高。HBM由于互联宽度超宽,这就决定了HBM的传输频率不能太高,否则总功耗和发热撑不住,所以延迟高(延迟指从读取指令发出,到数据准备就绪的过程,中间的一个等待时间)。

目前来说,CPU+DRAM技术较为成熟,成本相对较低,在多数对性能没有极端需求的场合具有更好的性价比,而GPU+HBM的组合则更多用于对算力要求特别高的应用领域。从2D走向3D,集成度更高、能耗效率更高的HBM是未来趋势,随着TSV工艺和HBM设计的不断成熟,HBM自身的性价比也会有所提升,将会逐渐占据更多的市场。

评论