数字接收机中位同步器的研制

摘要:位同步器在通信系统中有重要的作用,直接影响接收机的性能。基带成形滤波器对信号频谱进行压缩时,利用个位同步器消除码间干扰和提高系统频带利用率。本文为升余弦成形滤波器的数字接收机设计出一种简单可行的位同步器,并通过仿真验证了其简单性和可行性。

本文引用地址:https://www.eepw.com.cn/article/201608/296188.htm在数字通信中,基带数字信号波形是矩形脉冲,其上升沿和下降沿是突变的,因而高频成分丰富,频域占用的频带很宽。信号通过带限信道时,致相邻码元产生码间干扰,增大接收机发生错误的概率。基带成形滤波器可以在不增加信道带宽的情况下,减小码间干扰,降低基带信号的带宽,提高频带利用率。位同步器的作用在于确定提取各个码元定时脉冲的适宜时刻,可能是码元结束时刻、码元中间时刻或者其他时刻。平方根升余弦滤波器是应用较为广泛的成形滤波器。

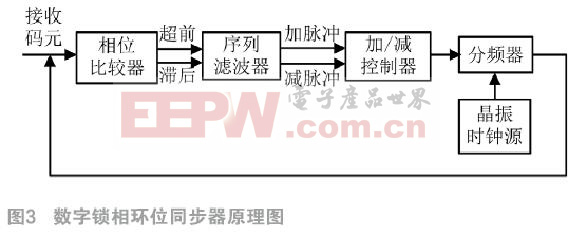

位同步指的是从收讯机基带信号中提取码元定时信号的全过程。位同步[1]是正确采样的基础,在数字接收机中的地位极其重要。实现位同步信息的方法通常有插入导频法和直接法两大类[2]。目前,直接法的应用范围较广。直接法是从接收的数字波形中提取它所携带的同步信息。在数字接收机中,主要采用直接法进行位同步的方法有:M&M算法、Gardner算法、平方率算法等。在传统的数字通信系统中,接收机的时钟同步和最佳判决取样时刻是通过模拟锁相环调整得到的。全数字接收机一般不能通过直接采样得到位同步的最佳时刻,必须利用位定时误差估计值控制内插滤波器对采样信号样本值进行插值运算,得到信号在最佳时刻的近似值。

本文所提的位同步算法是基于最大似然算法对于采用平方根升余弦滤波器作为成形滤波器系统,在接收端进行匹配滤波后,提取位时钟。

1 成形滤波器

1.1 成形滤波器原理

最初的成形滤波器设计是在频域上进行的,其过程是寻找一个普通滤波器来近似所要求形成的最终频谱的形状,然后用幅度均衡和群延时网络来校正。数字信号处理技术和超大规模集成电路技术的发展,利用数字滤波来实现频谱形成滤波的趋势越来越明显。尤其是对升余弦滚降滤波器的设计和研究更为全面。

升余弦滤波器具有如下优点[3]:

(1)满足Nyquist 第1准则;

(2)消除理想低通滤波器设计上的困难,有一平滑的过渡带;

(3)引入滚降系数改变传输信号的成形波形,减小抽样定时脉冲误差所带来的码间干扰。

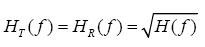

由通信原理可知,信道传递函数C(f)、成形滤波器传递函数HT(f)和接收滤波器传递函数HR(f)应满足:

![]() (1)

(1)

其中,![]() 在分段叠加后为理想低通函数。当信道为理想信道(即

在分段叠加后为理想低通函数。当信道为理想信道(即![]() )时,

)时,

(2)

(2)

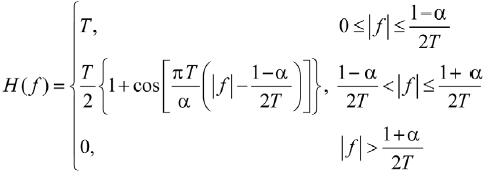

取H(f)为滚降的升余弦函数,其表达式如下:

(3)

(3)

其中,![]() 为滚降因子,T为符号周期。当

为滚降因子,T为符号周期。当![]() 时,H(f)是一个带宽为1/(2T)的理想低通滤波器。根据

时,H(f)是一个带宽为1/(2T)的理想低通滤波器。根据![]() 可得:

可得:

(4)

(4)

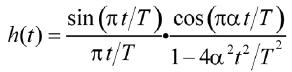

则平方根升余弦滤波器的时域表达式为:

(5)

(5)

1.2 基带成形滤波器的实现

随着数字信号处理硬件技术和超大规模集成电路技术的发展,利用数字式处理来实现频谱波形成形滤波器的情况越来越广泛。数字滤波具有精度高、可靠性高、灵活性强、便于大规模集成、高性能指标等优点,可实现有限冲激响应滤波器或无限冲激响应滤波器。由于数字技术的发展,基带信号的频谱成形可通过数字方法实现。常用方法有查表法和滤波法。在用FPGA实现时,查表法不但节省硬件资源,而且能提高系统实现的最高频率,以节省乘法器。对于时域函数,理论上是连续的,但在实际中,只要取有限样点即可。成形滤波器的采样速率一般要求比输入的基带信号速率要高(通常是其4~8倍)。因此,要先于脉冲成形的整数倍插值,以便信号卷积。

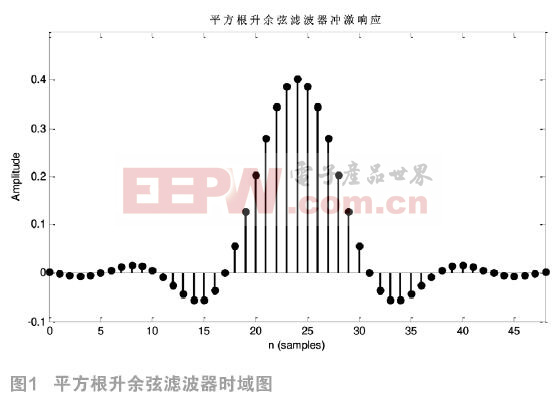

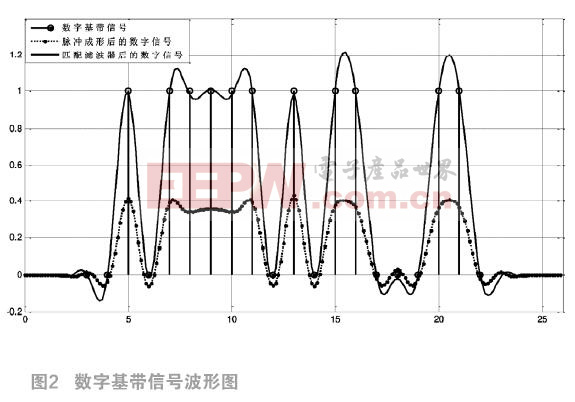

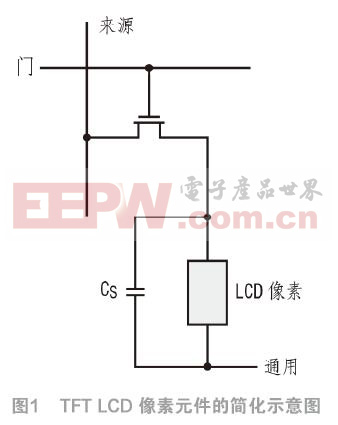

图1给出了![]() ,平方根升余弦滤波器的冲激响应。由图1可以看出,其波形没有陡峭的变化,因而,其高频分量比矩形波形明显减少。图2给出了基带数字信号、脉冲成形后的数字信号和接收匹配滤波器之后的时域波形图。这里成形滤波器采样速率是基带信号速率的8倍。

,平方根升余弦滤波器的冲激响应。由图1可以看出,其波形没有陡峭的变化,因而,其高频分量比矩形波形明显减少。图2给出了基带数字信号、脉冲成形后的数字信号和接收匹配滤波器之后的时域波形图。这里成形滤波器采样速率是基带信号速率的8倍。

2 位同步器

2.1 位同步原理

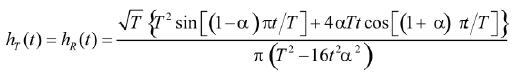

在实际的通信系统中,发射机的时钟速率和接收机的时钟速率不一定完全相同,可能会存在一定的偏差。因此,需要最大可能地降低或消除这种偏差带来的影响。实现位同步的主要方法有插入导频法和直接法。插入导频法是在基带信号频谱的零点处插入所需的位定时导频信号,在接收端使用一个窄带滤波器,从接收信号中提取出位同步时钟,将接收信号通过移相、倒相和相加电路来消除导频信号对进入取样判决器的基带信号的影响。直接法是直接从接收的数字信号中提取位同步信号,主要提前-滞后门同步算法和锁相环法。提前-滞后门是利用波形信号的对称性,根据接收信号经过匹配滤波器或相关器的输出值是采样值的相对大小来判断是否同步和调整方向。锁相环法是采用时钟误差信号控制压控振荡器,实现时钟相位误差调整,直接采样就可以获得接收信号的近似最佳采样点。在数字接收机中,由于采用固定频率的时钟进行采样,所以当抽样时钟与数据码元不同步时,可以通过在非同步的抽样数据之间进行内插,以得到同步的信号值点。

本文来源于中国科技期刊《电子产品世界》2016年第8期第46页,欢迎您写论文时引用,并注明出处。

评论