数字接收机中位同步器的研制

数字锁相环[4](DPLL)位同步器具有体积小、成本低、可靠性高等优点,避免了模拟器件所固有的温漂、VCO非线性、器件易饱和等缺点,因而在同步数字通信系统中得到广泛的应用。数字锁相环位同步器原理框图如图3所示。

本文引用地址:http://www.eepw.com.cn/article/201608/296188.htm数字锁相环主要由高稳定的晶振、分频器、相位比较器、序列滤波器和控制器组成。位同步时钟由晶振和分频器分频后产生。如果位时钟信号超前于接收码元相位跃变时,则扣除脉冲门减去一个计数脉冲,进而使本地时钟相位减少一个时间间隔。这个时间间隔是由分频器的最小时间间隔决定。相反,则加上一个计数脉冲,使本地时钟前进一个时间间隔。这种方法的优点是不需要专门提供位同步信号,缺点是接收基带信号不能出现长串“0”和“1”,否则会导致锁相环失锁。图3中的序列滤波器可以滤除噪声的干扰,降低由转换时间产生的随机抖动。数字锁相环是目前使用较多的一种技术,具有工作频率高、宽带宽、频谱质量好、控制灵活、体积小和成本低等优点,但是其频率分辨率低、频率建立时间长、相位噪声性能较差和码率适应性差。全数字接收机的插值法位时钟恢复的结构框图如图4所示。

要计算出正确的内插值,需要知道正确的插值基点和小数插值间隔,这是由插值控制器来计算[4-5]的。理想的插值滤波器是非因果的,物理上是不可实现的。因为它需要无穷多个信号样值点。实际上,也没有必要在解调中完全恢复接收信号r(t)的任何时刻的值。常用的内插滤波器有线性内插器、拉格朗日内插器和最佳低通滤波器构成的内插器。线性内插器要求两个样值点参与运算,而拉格朗日内插器需要多个样值点参与运算,所以拉格朗日内插器性能要优于线性内插器。多项式内插器适合基带信号的样点速率超出其奈奎斯特速率多倍的情况,而由最佳低通滤波器构成的内插器更适合于基带信号的样点速率大于其奈奎斯特速率的情况。

2.2 简单数字位同步器的设计

直接法提取位同步时钟的方法主要是通过接收数据有码元0和1变换进行计算得到码元最佳采样时刻。由图1和图2可以看出,平方根升余弦成形滤波器近似为Sinc函数,经过脉冲成形后的码元数据近似为升余弦的形状。对于单个码元1来说,理想情况是采样时刻是成形滤波器最大值。在FPGA实现时,运算速度和精度会限制其性能。特别是,通过内插来恢复数字位同步时钟的方法运算量大,所占硬件资源多,会限制芯片的应用。

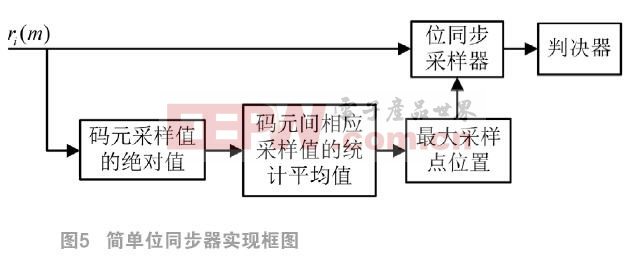

假设接收端第i个码元的数字信号表示为![]() ,对每个码元的采样点数M进行统计求取最大值作为这个码元的最佳采样点,送入判决器。具体实现如图5所示。

,对每个码元的采样点数M进行统计求取最大值作为这个码元的最佳采样点,送入判决器。具体实现如图5所示。

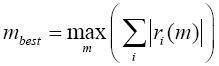

在图5中,最佳采样点位置 。

。

3 仿真结果

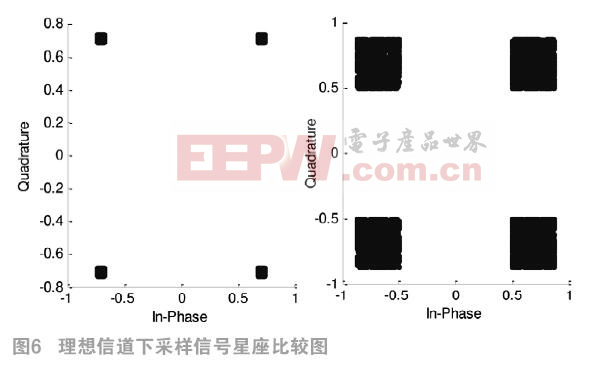

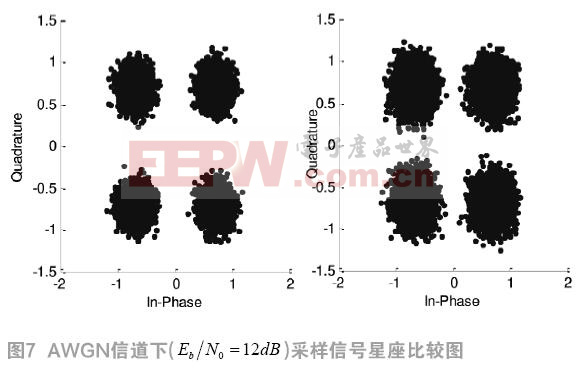

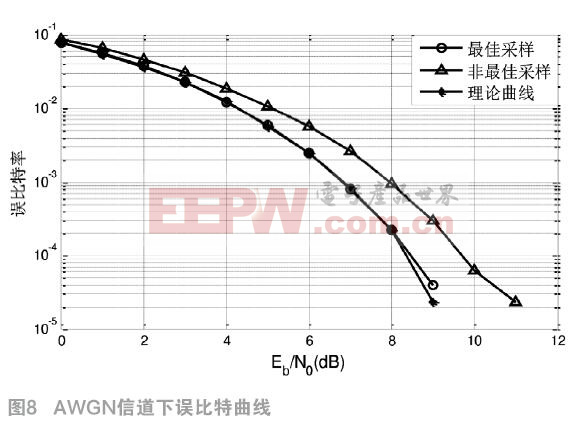

多进制移相键控(MPSK)具有较高的频带利用率,在高数据率通信系统中得到广泛的应用。对所涉及的简单位同步器在QPSK通信系统中进行仿真,码元周期为0.1μs,每个码元采样率是码率的8倍,平方根升余弦滤波器采用如图1所示(滚降因子为0.5)设计,一帧数据包含128个符号,这里对每帧数据进行统计来寻找最佳采样点。图6和图7分别给出了理想信道和![]() 加性高斯白噪声信道下基带信号经过匹配滤波器后的最佳采样信号(左图)和偏移最佳采样点一个位置的信号星座图(右图)。由图6和图7可以看出,最佳采样的信号星座图比非最佳采样的信号星座图更紧凑。这也证明了最佳采样位置的正确性。

加性高斯白噪声信道下基带信号经过匹配滤波器后的最佳采样信号(左图)和偏移最佳采样点一个位置的信号星座图(右图)。由图6和图7可以看出,最佳采样的信号星座图比非最佳采样的信号星座图更紧凑。这也证明了最佳采样位置的正确性。

对QPSK系统的性能仿真图如图8所示。由图8可以看出,所提到的位同步器误比特曲线与理论曲线相重合,并无性能损失。而非最佳位置采样的误比特率比最佳位置采样的误比特损失约1dB。因此,这种同步方法具有可实现性和正确性。

4 结论

本文所提的位同步算法是直接从数字信号中提取位同步信号,而不需要数字锁相环和插值滤波器等模块,因而具有实现简单,复杂度低,性能优良等特点。但是,这种位同步器的应用具有一定的局限性,它只能用在具有脉冲成形模块和接收端高倍采样的系统中。

参考文献:

[1]姜宇柏,游思晴.软件无线电原理与工程应用[M].北京:机械工业出版社,2007.

[2]樊昌信,张甫翊,徐炳祥,等.通信原理(第5版)[M].北京:国防大学出版社,2006.6.

[3]张公礼.全数字接收机理论与技术[M].北京:科学出版社,2005.

[4]Floyd M.Gardner.锁相环技术(第3版)[M].北京:人民邮电出版社,2007,11.

[5]Floyd M Gardner. Interpolation in digital modems part I: fundamentals. IEEE Trans Comm., 1993,41(3):501-507.

[6]Erup L and Gardner F M and Harris R A. Interpolation in digital modems part II: implementation and performance. IEEE Trans Comm., 1993,41(6).

本文来源于中国科技期刊《电子产品世界》2016年第8期第46页,欢迎您写论文时引用,并注明出处。

评论