基于FPGA的高速数据传输研究

摘要:大数据发展如火如荼,解决串行数据高速传输已成当务之急。本文正是以此为出发点,介绍了Xilinx FPGA内嵌的高速串行收发器RocketIO。测试结果表明,RocketIO收发器的传输速度最高可达6.6Gbps,可以完全胜任各种高速数据的传输与处理。

本文引用地址:http://www.eepw.com.cn/article/201608/296187.htm引言

近年来,电子行业的发展走进了黄金时期,优势明显的串行传输无论在速度上还是信号完整性上都得到了飞速发展。无论高速AD采样后的数据接收,还是高速实时数据的传输与处理,都离不开高速串行总线。尤其对大型的采集系统,往往需要在单位时间里采集到成百上千个高精度的实时数据,这就要求在进行串行传输时速率达到百兆,甚至千兆每秒的级别。而Xilinx FPGA所提出的RocketIO 正是一种完全可以满足当前需求的解决方案。

本文主要介绍了RocketIO GTX的原理,并在此基础上提出设计中需要注意的设计要点,最后进行了板间高速数据传输的测试,给出了实时数据的采样波形图。

1 RocketIO GTX收发器介绍

RocketIO GTX是Xilinx公司FPGA内嵌的一种可配置的高速串行数据收发器,其传输速度在600Mbps~6.6Gbps[4]。该公司Virtex-5与Virtex-6系列FPGA都内嵌了RocketIO GTX,且其结构和工作原理也基本相同[1],本文将以Virtex-6 系列FPGA内嵌的GTX为重点进行介绍。

1.1 RocketIO GTX主要特点

● 每个通道收发器支持从600Mbps~6.6Gbps的全双工传输速率;

● 收发器内嵌发送时钟生成电路和接收时钟恢复电路;

● 差分输出端5级可配置电压(110mV~1130mV);

● 发送端支持可编程预加重/去加重,和判定反馈均衡(DFE);

● 支持可编程差分输出电压摆幅(110mv~1130mv)和可编程预加重;

● 收发器支持直接和交流耦合方式,可兼容多种高速接口标准;

● 片内集成可编程差分终端电阻;

● 支持片内多种环回测试模式;

● PCS集成多种可选编码功能,如comma字符对齐、8B/10B编码、时钟修正和通道绑定[2]。

1.2 RockerIO GTX内部结构

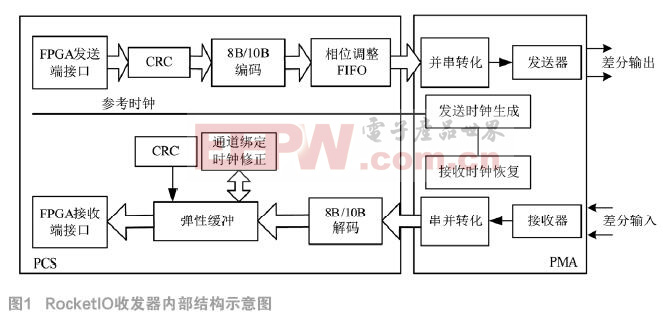

RocketIO GTX收发器由两部分组成:PCS(Physical Coding Sublayer)和PMA(Physical Media Attachment,物理媒介层),如图1所示。

其中 PMA部分主要包括串行和解串器、发送和接收驱动器、时钟产生和恢复单元;PCS 部分主要包括 8B/10B 编解码、通道绑定、时钟修正和 CRC校验模块。

● 8B/10B 编解码

8B/10B编码机制是进行高速串行传输时普遍采用的编码方式,其实现原理是将8位字符根据对应码表转化为10位字符,这种转换保证了通道的直流平衡性,有利于交直流耦合,提高信道传输质量。

● 通道绑定

通道绑定(Channel Bonding),一种通过一定协议将多个串行通道绑定达到并行传输,目的在于实现对数据吞吐率增大的技术。绑定原理是,在所有并列的串行通道中,定义一个主通道,其它均为从通道,主通道发送同步使能信号来与其它从通道进行对齐,从而解决各个通道数据同步问题,实现串行通道的并行绑定。

● 串行器和解串器

在发送端,收发器把输入GTX的参考时钟作20倍频,作为发送线路的参考时钟,然后将经过编码的并行数据转化为串行数据,从串行差分端发送出去;在接收端,时钟恢复电路从比特流中提取出时钟相位和频率,恢复出接收时钟,将串行数据解码并转化为并行数据,送入用户接口以进行其他操作。

● 时钟修正

时钟修正(Clock Correction)目的在于发送端与接收端的时钟匹配,在收发器的TX端,对要发送的串行数据中插入特定的修正序列,RX端通过这些修正序列提供的信息对时钟进行修正。

2 RocketIO GTX设计要点

要使RocketIO模块以最佳性能工作,实际设计中需要考虑到诸多设计因素,本节将对设计中经常遇到的问题进行讨论。

2.1 参考时钟

高速串行数据的传输中,为了实现高速,对时钟的要求当然就更为苛刻,这就要求用来驱动收发器的时钟必须具备高性能、低抖动的特点。一般来讲,GTX收发器提供了3种参考时钟的驱动方式:

①从外部GTX专用时钟端口输入来驱动时钟路由;

②从相邻Quard的专用时钟路由获取;

③从FPGA内部获取。

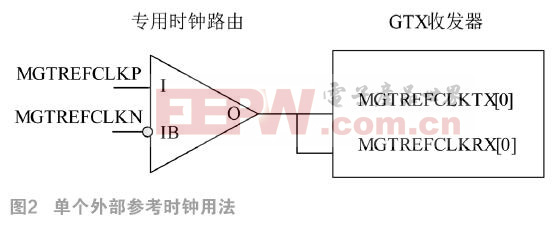

每个Quad中都拥有两个专用差分时钟输入MGTREFCLK0[P/N]和MGTREFCLK1[P/N],它们是时钟源的接口,为整个GTX的时钟提供保障。在设计中,当选用这种方式的时钟供应时,需要对原语IBUFDS_GTXE1进行例化。需将原语IBUFDS_GTXE1的输出做为GTXE1的端口MGTREFCLKTX[0]和MGTREFCLKRX[0]的输入。需要注意的是,即使在设计中未使用TX PLL,MGTREFCLKTX[0]仍然需要被连接[5]。单个外部参考时钟用法如图2所示。

前两种参考时钟的驱动方式都是使用GTX所集成的专用时钟路由,在精度上能得到很好的保障。第三种由内部全局时钟网络提供,会引入更大的抖动,而且驱动能力也有限,因此要尽量避免使用。

2.2 用户时钟

GTX的接收端和发送端都有两个用户时钟,这里以发送端为例进行介绍。这两个时钟分别为:TXUSRCLK和TXUSRCLK2。其中TXUSRCLK2是发送端TX的用户时钟,允许用户直接使用,由GTX的内部时钟TXOUTCLK驱动。用户将并行数据传输到发送接口,在用户时钟上升沿被采样并送入发送缓冲,经过编码以及串行化之后发送出去。TXUSRCLK是PCS内部逻辑时钟,不允许用户直接使用,其大小取决于如下公式[3]:

![]()

由于在设计中通常会选择8B/10B编码,因此16bit并行数据经过编码后变为20bit。这里需要注意的是,需要设置属性GEN_TXUSRCLK=TRUE。此时,TXUSRCLK端口必须拉低,逻辑时钟TXUSRCLK由GTX内部提供,并且用户时钟TXUSRCLK2大小与TXUSRCLK相同[4]。当设计中线速率选为3Gbps,可知用户时钟TXUSRCLK应为150MHz。时钟结构如图3所示。

GTX的接收端RX与TX基本相似,也包括两个用户时钟分别为:RXUSRCLK和RXUSRCLK2。其中,RXUSRCLK2是GTX接收端的用户时钟,由恢复时钟RXRECCLK驱动。RXUSRCLK的驱动方式和属性设置与发送端一致[5]。

2.3 Comma 检测对齐

Comma检测对齐模块是高速数据传输中必不可少的重要模块,高速数据的识别对齐是传输中的核心问题。在RX接收模块中,串行数据转换为并行前,必须经过边界字符对齐才能对所传输的数据进行识别,才能有后续的并行数据。在实现高速串行信号发送时,TX端会先发送comma字符,然后再发送数据。对应的RX接收端通过comma探测,当检测到comma字符后,需要进行对齐,然后接收数据[6]。

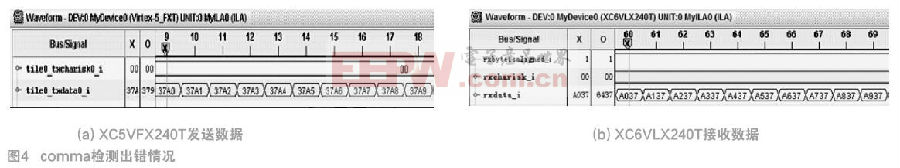

GTX收发器的comma模块在实际解码应用中通常选K28.1、K28.5和K28.7为comma字符,具体根据项目需求来选择。设计中,为了确保数据的对齐,通常会选择发送2000个左右的同步字符。在TX端发送K字符时,赋值TXCHARISK=2’b01,TXDATA=16’h43BC。这里TXCHARISK=2’b11表明对应数据的低字节为K字符,对应比特流中的comma字符。需要注意的是,当TXCHARISK=2’b11,发送TXDATA=16’hBCBC时,由于TXDATA中高八位和低八位相同,这样在接收端容易出现错位8位的情况。如图4所示。

造成这种情况的原因是,在进行K字符探测对齐的过程中,将两个K字符的低字节和下一个的高字节组合,这样探测对齐系统会认为实现了对齐过程,在接下来的数据接收过程中会以这种方式进行对齐。

3 应用系统

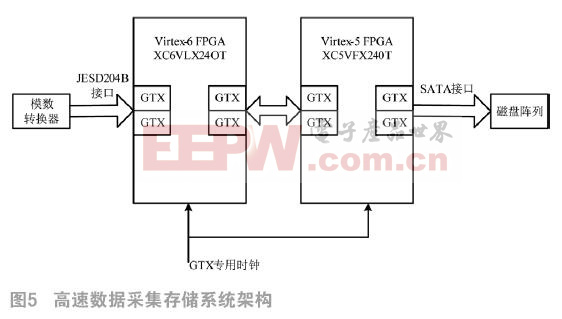

基于RcoketIO GTX的高速串行传输,设计出了一个高速数据采集存储系统,采集端使用XC6VLX240T,存储端使用XC5VFX240T。由图5可以看出,ADC的高速数据是通过其自带JESD204B接口与V6实现GTX互联的,V6与V5两FPGA间的数据传输也采用GTX传输,后面SATA设计中还是使用GTX来实现的。

从数据流来看,AD将采集的高速数据通过GTX(配置成JESD204B接口)送入Virtex-6,经过一定的数据处理后通过GTX发送至Virtex-5 FPGA,最终通过GTX(配置成SATA接口)存入磁盘阵列。由此可见,RocketIO GTX是整个系统中高速数据传输的核心。

4 实验结果和分析

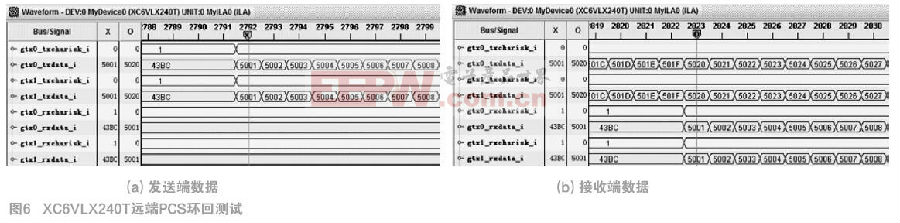

通常对系统设计中GTX通路的连接需要进行测试,以下将通过本V6端的PCS远端测试来验证其工作性能,也就是V6端发送测试数据至V5然后通过PCS环回至V6接收端,来看数据的正确与否。chipscope采样如图6所示。

由于远端PCS环回模式可以同时测试两端GTX的通信情况,故由图6可知,XC6VLX240T、XC5VFX240T可以正常通信。

高速数据传输中,经常要对数据进行各种转换,而数据的拼接与拆分是最常用的手段,图7是对一路 0000-FFFF的递增码,将递增码拆分成两路分别为4K数据和43BC。也就是将一个递增码分成TRIG1和TRIG2的两路GTX数据进行发送来测试数据的正确性。

由数据总线图可以看出,两路数据成完美递增状态。

5 结束语

本文以高速数据传输为出发点,介绍了基于RocketIO GTX 的解决方案,并给出了以GTX为核心的应用系统设计。由此可见,采用 RocketIO收发器进行高速串行数据的传输,在保证速度的前提下,传输过程中的信号完整性也得到了极大的保障,为高速数据的传输提供速度和质量上的保证 。

参考文献:

[1]Xilinx. Virtex-6 Family Overview[M]. USA:Xilinx, 2012.

[2]Xilinx. Virtex-6 FPGA GTX Transceivers User Guide[M]. USA:Xilinx,2011.

[3]李大鹏,陈长胜,王世奎等.基于FPGA的高速串行传输接口研究与实现[J]. 航空计算技术,2008,38(2):100-103.

[4] Abhijit Athavale,Carl Christensen.High-Speed Serial I/O Made Simple[J].USA:Xilinx

Corporation.2005.4.

[5]徐文波,田耘.Xilinx FPGA 开发使用教程[M].北京:清华大学出版社,2012.7. [4] Xilinx.Virtex-5 FPGA [6]RocketIO GTX Transciver Wizard v1.5 Getting Started Guid[S].USA:Xilinx,2008

本文来源于中国科技期刊《电子产品世界》2016年第8期第42页,欢迎您写论文时引用,并注明出处。

评论