基于FPGA的RS编码器的设计与实现

RS编码是一种线性的块编码,其表示形式为RS(N,K)。当编码器接收到一个数据信息序列,该数据信息序列被分割成若干长度为K的信息块,并通过运算将每个数据信息块编码成长度为N的编码数据块。在RS码中的码元符号不是二进制而是多进制符号,其中2m进制使用更为广泛。能纠正t个错的RS码具有,如表1参数所示。上述参数,t表明最多可以纠正t个随机错误符号。

由于RS码是对多进制符号纠错,RS码可用于纠正突发错误,比如能纠两个八进制符号错误的RS(7,3)码,每个符号可用3 bit二进制符号表示。八进制的RS(7,3)码相当于二进制的(21,9)码,因此纠两个符号就相当于纠连续6 bit二进制符号的突发错误,然而二进制的(2l,9)码却没有纠6 bit突发错误的能力,它能纠任何2个随机错误以及长度≤4的突发错误。

通用的RS编码的运算步骤:

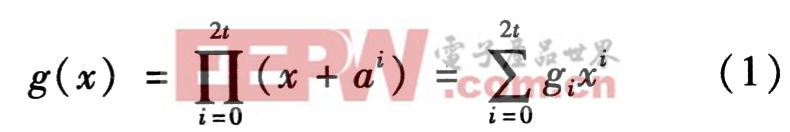

(1)确定RS编码器的生成多项式g(x),这里选用了最为常用的生成多项式,如式(1)所示。

式中a定义为m阶初等多项式p(x)的根它可生成全部GF域的元素。(有关GF域的内容可参阅相关书籍)。

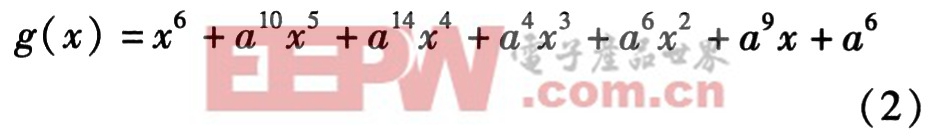

以RS(15,9)为例,RS(15,9)的生成多项式,如式(2)

(2)通过对取模运算产生校验信息多项式p(x)如式(3)

![]()

式中m(x)表示RS编码码字中的数据信息,它是K一1阶的线性多项式。

(3)通过加法运算生成最终的编码后的多项式c(x)如式(4)

![]()

RS码的编码主要是围绕码的生成多项式g(x)进行的,一旦生成多项式确定了,则码就完全确定了。

2 RS编码的设计实现

在一些特定应用域中,RS码的设计与实现是比较困难的。RS码是在有限域上进行的代数运算,不同于常用的二进制系统,实现相对复杂一些,其复杂度主要决定于有限域的大小、码字的长度、采用的编码算法等,编码器的实现方式主要有以下几种:

(1)微处理器实现的RS编码。

通用的微处理器采用查表(Table―lookup)方法可以实现RS编码,首先需要产生有限域运算中的系数,存于内存中,就可以通过查表的方法实现编码了。

(2)利用DSP实现的RS编码。

DSP早已成为传统微处理器的一种替代品,现在的DSP芯片已能对一些特定的应用提供并行的处理结构,可以在DSP芯片中完成RS编码,不过DSP不是专为实现纠错中需要的特定功能设计的,同样也可以采用查表的方法在DSP中实现快速有限域运算。

(3)ASIC实现的RS编码。

ASIC是专用集成电路,由LSI―Logic Corpera―tion设计的ASIC芯片,有3 kB的RAM和4 kB的ROM,是实现高速编码器的最佳选择。

(4)FPGA实现的RS编码。

FPGA能够快速和经济地将电路描述转化为硬件实现,而且对设计的修订也比较方便。而通常的ASIC需要的设计时间较长,制作费用也较高,也不便于调整。所以本设计是基于FPGA的RS编码设计。

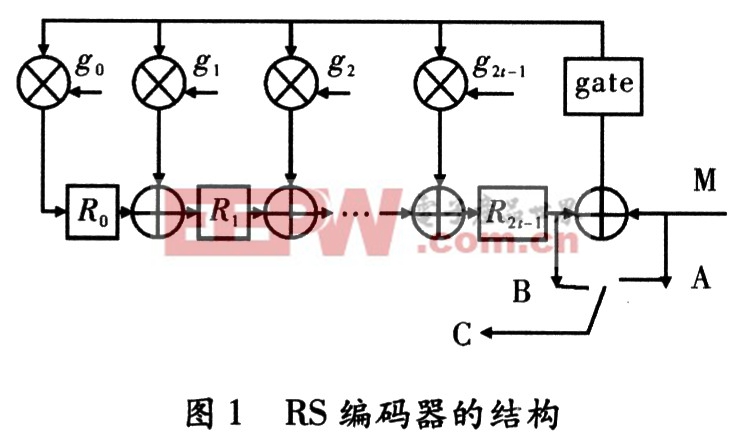

如图1所示为本设计所采用的编码器的结构。

其工作原理如下:

(1)寄存器R0~R2t-1全部清零。开关接通A点,然后信息位分为两路送电路中,一路直接送入C(x),一路送入除法电路并进行移位。每一个时钟移一个字节;

(2)在k个时钟结束的时候,信息位全部输入,完成除法功能。此时移位寄存器里保留了余式r(x)的系数,这就是RS码的校验位;

(3)在k+1个时钟到来的时候,开关接通B点。寄存器中的数据依次移出,送入信道。在经过2t个时钟后数据全部移出,得到2t个校验位。这2t个校验位跟在原先的尼个信息位的后面,组成(n,k)码输出。这样就完成了RS码的编码;

(4)寄存器R0~R2t-1全部清零,重复步骤(1)、(2)、(3),完成对下一组RS码的编码。

评论