基于FPGA的全数字锁相环的设计

锁相环(PLL)的理论与研究日趋完善,应用范围遍及整个电子技术领域,如信号处理,调制解调.时钟同步,倍频,频率综合等都应用到了锁相环技术。随着集成电路技术的发展,集成锁相环和数字锁相环技术日趋成熟,不仅能够制成频率较高的单片集成锁相环路,还可以把整个系统集成到一个芯片上去,实现所谓的片上系统SOC。因此,可以把全数字锁相环路(ADPLL)作为一个功能模块嵌入SOC,构成片内锁相环。这里在简单介绍片内全数字锁相环系列结构的同时,给出一种智能控制捕获范嗣中全数字锁相环(ADPLL)的设计方法,并进行仿真和实践验证。

2 ADPLL的结构及工作原理

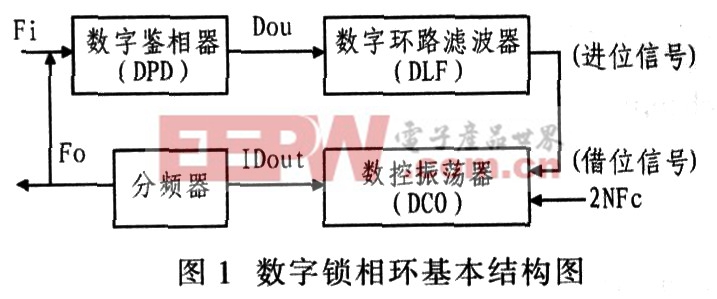

图1给出全数字锁相环(ADPLL)的基本结构。主要由数字鉴相器DPD,数字环路滤波器DLF,数控振荡器DC0,分频器4部分组成,其中心频率为fc。DPLL是一种通过相位反馈来控制系统的电路结构。根据输入信号Fin和本地时钟输出信号Fout之间的相位误差信号送入数字环路滤波器,并对相对误差进行平滑滤波,生成控制信号carry和bor―row,数字振荡器根据控制信号调节反馈,使输出信号Fout的相位逐渐跟踪输入信号Fin的相位,最终达到锁定。

3 ADPLL各模块的功能和具体实现方法

3.1 数字鉴相器

常用的鉴相器有2种类型:异或门(X0R)鉴相器和边沿控制鉴相器(ECPD),设计中采用异或门鉴相器。异或门鉴相器用于比较输入信号Fin和输出信号Fout之间的相位差,并输出误差信号Dout,Dout作为计数的方向信号输入给下一级。

3.2 数字环路滤波器

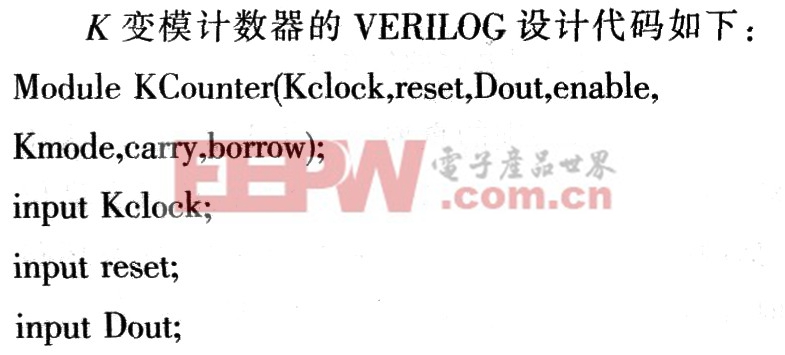

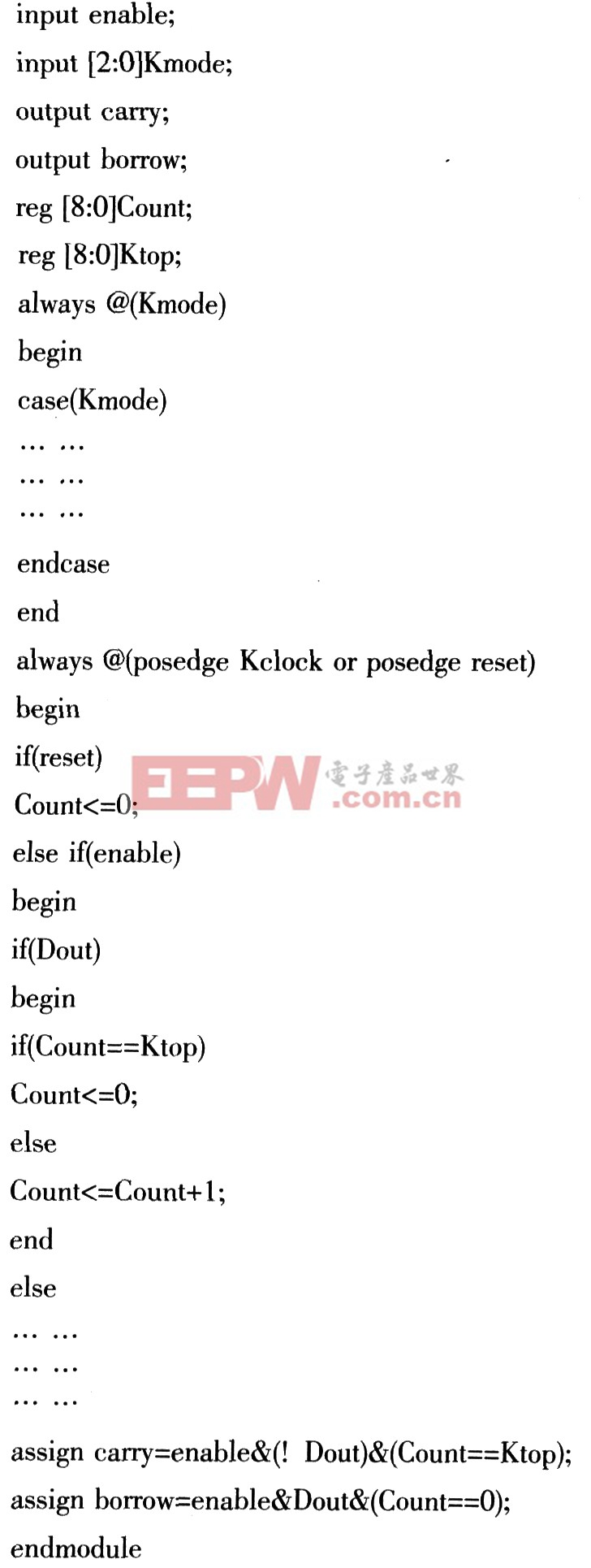

数字环路滤波器(DLF)由一个模值为变量K的可逆计数器来实现。其作用首先用于消除数字鉴相器输出的相位误差信号Dout中的高频分量,保证锁相环路性能的稳定性和准确性:其次K变模计数器再根据鉴相器的相位误差信号Dout来进行加减运算。若Dout是高电平时,计数器进行加运算,直到相加结果达到预设模制K,则环路滤波器输出一个进位脉冲信号carry给数控振荡器;若Dout是低电平时,计数器在模值K的基础上进行减运算,直到为零,并输出一个借位信号borrow给数控振荡器:当环路锁定或只有随机干扰脉冲时,Dout是一个占空比为50%的方波,即计数器的加减数目基本相等,计数结果在K附近上下徘徊,不会产生进位或借位脉冲,大大减少了由随机噪声引起的对锁相环路的误控。也就是说,采用K计数器作为滤波器,有效的滤除了噪声对环路的干扰。

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理 鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论