基于FPGA的RS编码器的设计与实现

本文引用地址:http://www.eepw.com.cn/article/192144.htm

4 RS编码器的仿真

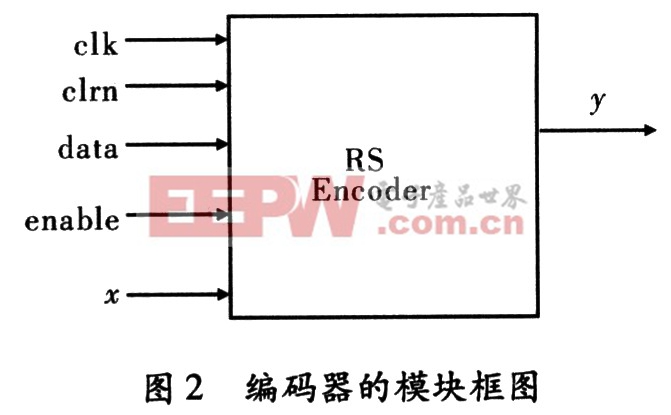

本设计是实现了RS(15,9)的编码,本设计编码器的模块框图,如图2所示。

各信号说明如下:

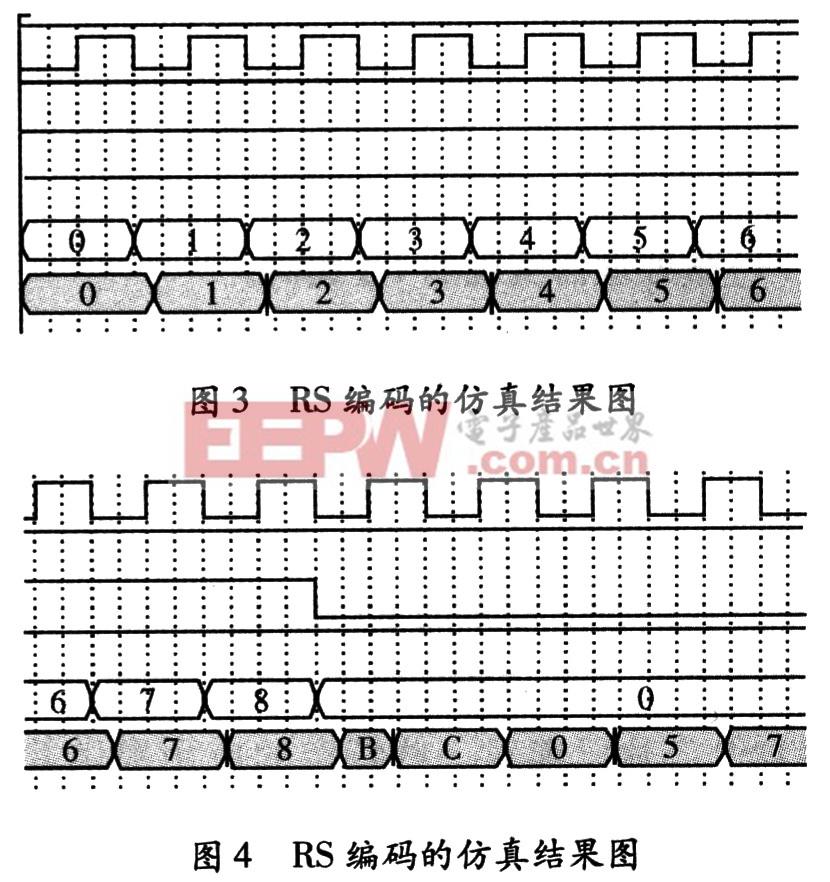

本设计信号时钟clk周期是40 ns,clrn是复位号,data表示信息输入有效,enable表示启动编码器,开始编码,x是4 bit信息符号,y是编码生成的4 bit码字。由下图编码图形可知,一次编码周期需要590.0 ns,最大编码速率为l700 MHz。因此,一次编码需要15个时钟周期。在25 MHz的时钟下,RS编码器仿真时序图,如图3和图4所示,并由仿真图可看出,本算法的编码速度高时延间隔不到半个周期。

RS编码测试数据如下:

输入信息:0,1,2,3,4,5,6,7,8;

编码器输出:0,1,2,3,4,5,6,7,8,B,C,0,5,7。

5 结束语

RS编码的所有运算都是建立在有限域的基础上的,其中乘法器的设计是其编码技术的关键。本设计实现了RS(15,9)的编码设计和仿真,仿真输出结果与理论分析一致,基于相同的原理,可以实现任意数据块长度的RS编码器设计。

评论