改进型CIC抽取滤波器设计与FPGA实现

摘 要:为了改善级联积分梳状(CIC)滤波器通带不平和阻带衰减不足的缺点,给出一种改进型CIC滤波器。该滤波器在采用 COSINE滤波器提高阻带特性的基础上,级联了一个SINE滤波器,补偿了其通带衰减。硬件实现时,采用新的多相分解方法结合非递归结构,不仅大大减少了存储单元数量,还使电路结构更加规则。经仿真和FPGA验证,改进型CIC滤波器使用较少硬件,实现了阻带衰减100.3 dB,通带衰减仅为O.000 1 dB 。

关键词:CIC抽取滤波器;COSINE滤波器;SINE滤波器;设计优化;FPGA

抽取滤波器是∑-△模/数转换器中的重要组成部分,积分梳状滤波器经常作为第一级滤波器,用以实现抽取和低通滤波。其优点是实现时不需要乘法器电路,且系数为整数,不需要电路来存储系数,同时通过置换抽取可以使部分电路工作在较低频率,与相同滤波性能的其他FIR滤波器相比,节约了硬件开销。经过仿真,抽取率为32的一阶积分梳状滤波器第一旁瓣相对于主瓣的衰减最大约为15 dB,这样的阻带衰减根本达不到实用滤波器的设计要求。为了改变滤波性能,一般采用级联积分梳状滤波器(CIC)。但经过CIC降频滤波系统降频后会产生信号混叠现象,并且主瓣曲线不平,需要用新的算法或新结构来修正改善这些特性。

1 CIC抽取滤波器原理

经典的抽取滤波器为Hogenauer CIC滤波器,其传输函数表达式为:

式中:参数M为降频因子,决定了CIC的通带大小;K为滤波器的阶数,对阻带衰减起到加深作用。频率响应为:

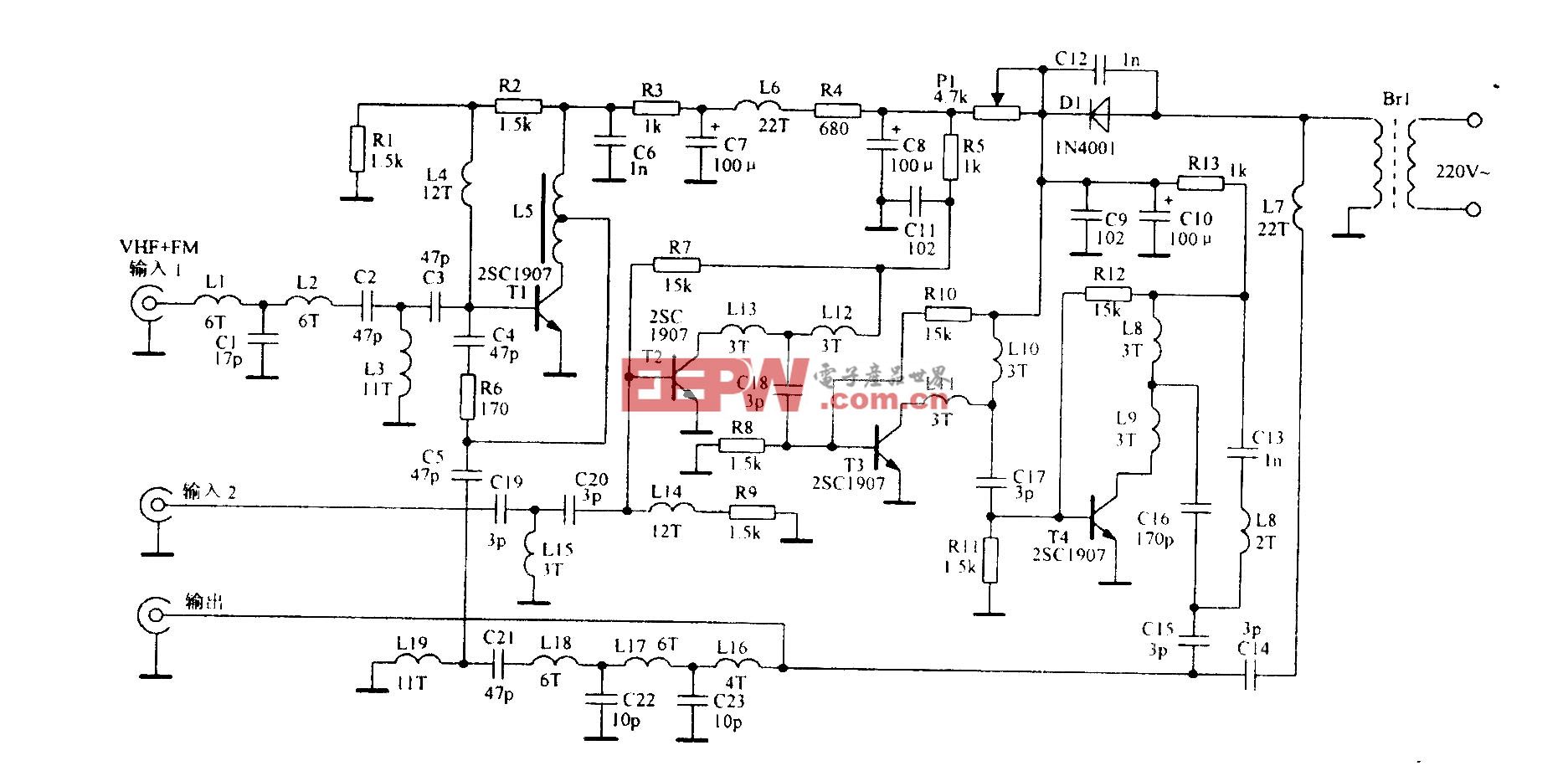

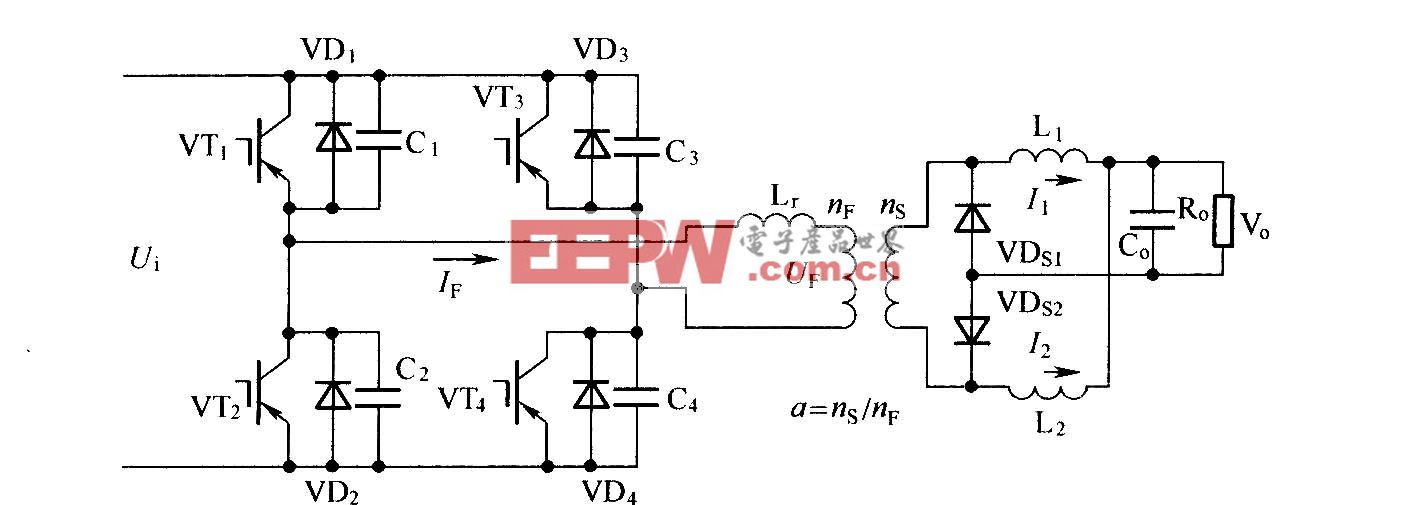

滤波电路由积分模块与差分模块组成,根据置换原则将抽取因子提到差分模块之前,使其工作在较低频率,并节省了M-1个存储单元,框图如图1所示。

2 改进的CIC结构

为了改善CIC抽取滤波器阻带衰减不足的缺点,采用一种新型COSINE滤波器,其传输函数为:

当N取不同值时,幅频响应如图2(a)所示。

把不同N值的COSINE滤波器级联,幅频响应会呈现低通特性,因此文献[4]采用CIC滤波器级联COSINE滤波器的结构来改善传统CIC滤波器的幅频特性。令Ni=M/2i+1,此时COSINE滤波器第一个零点与CIC滤波器的第一个零点重合,增加了第一个零点附近旁瓣的衰减。取M=32,传输函数为:

![]()

评论