改进型CIC抽取滤波器设计与FPGA实现

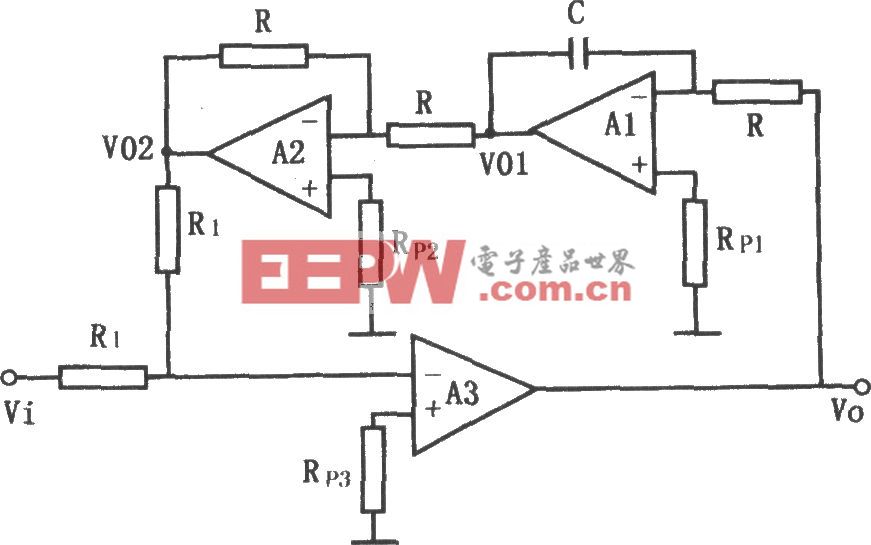

图2(b)为M=32的四阶CIC滤波器与新结构的滤波器(CCOS)幅频响应对比。式(5)中取k1=4,k2=k3=2;n1=2,n2=n3=4。从图2中可以看出CIC滤波器第一旁瓣相对于主瓣衰减为52.94 dB,而CCOS的旁瓣衰减则达到101.9 dB。如果达到相同的阻带衰减,CIC至少高达8阶,其实现电路将会非常庞大。本文引用地址:http://www.eepw.com.cn/article/192006.htm

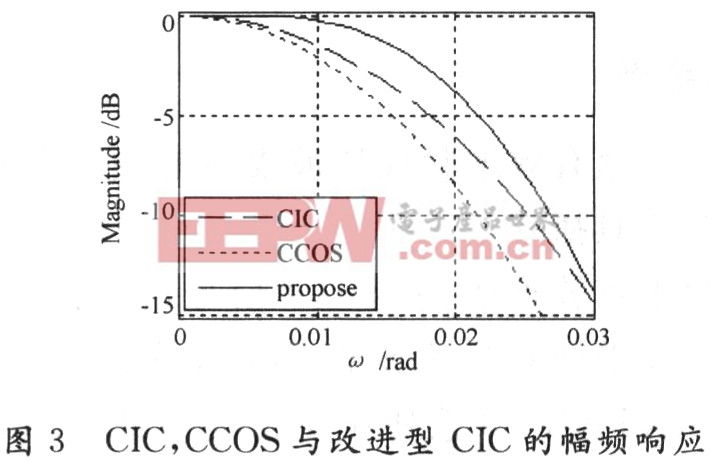

图2(c)对上述两种滤波器主瓣曲线放大,从图中明显可以看出CCOS滤波器通带特性比CIC变差。取滤波器的通带截止频率为fc=1/8M(Fs为归一化值),CIC通带衰减为O.129 3 dB;CCOS为0.286 7 dB。

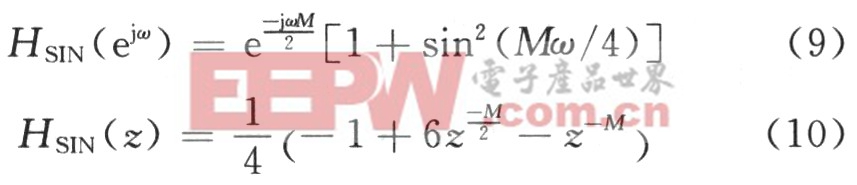

为了进一步提高CCOS的通带特性,对文献[4]提出的CCOS进行改进,在其后级联一个SINE滤波器,其幅频特性与传输函数如下:

式中:M必须为偶数,这样才能避免分数延时。出于节省功耗的目的,取M为抽取值的2倍,这样SINE滤波器即可在提取到抽取之后,将计算量降为原来的 1/M,该结构通过移位和加法即可实现,无需乘法器。图3为改进型CIC(取M=64)与CCOS,CIC的幅频特性曲线比较,可以看出改进的CIC滤波器的通带特性得到明显改善。由于补偿滤波器的引入,阻带衰减为100.3 dB,但通带衰减仅为O.000 1 dB.

3 改进型CIC的FPGA实现

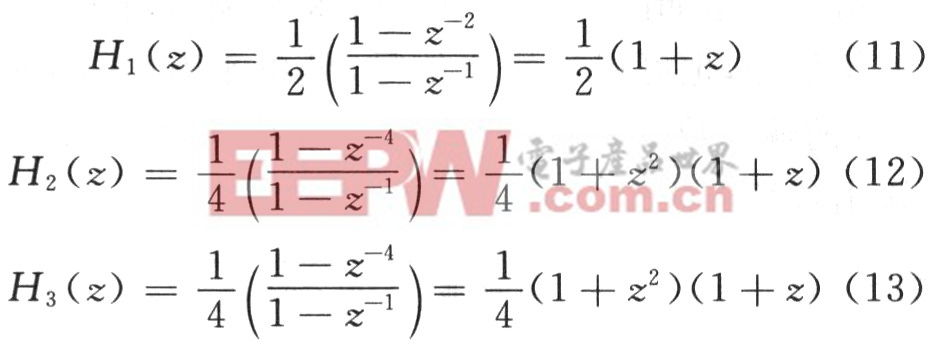

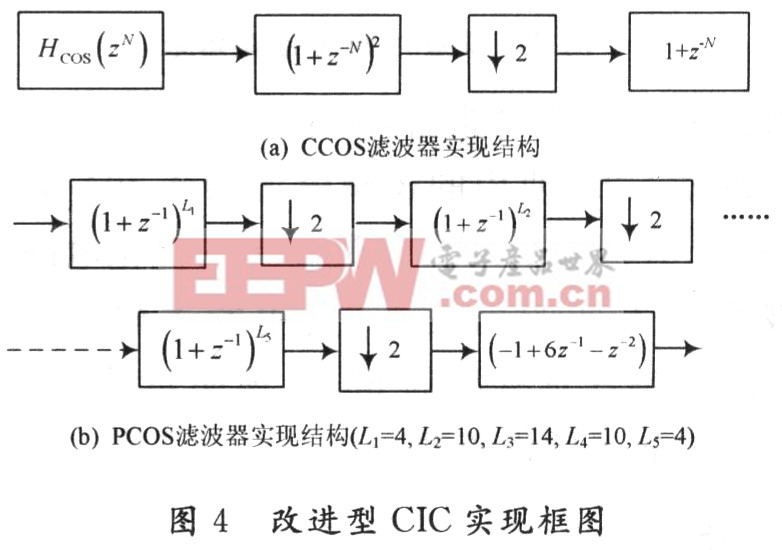

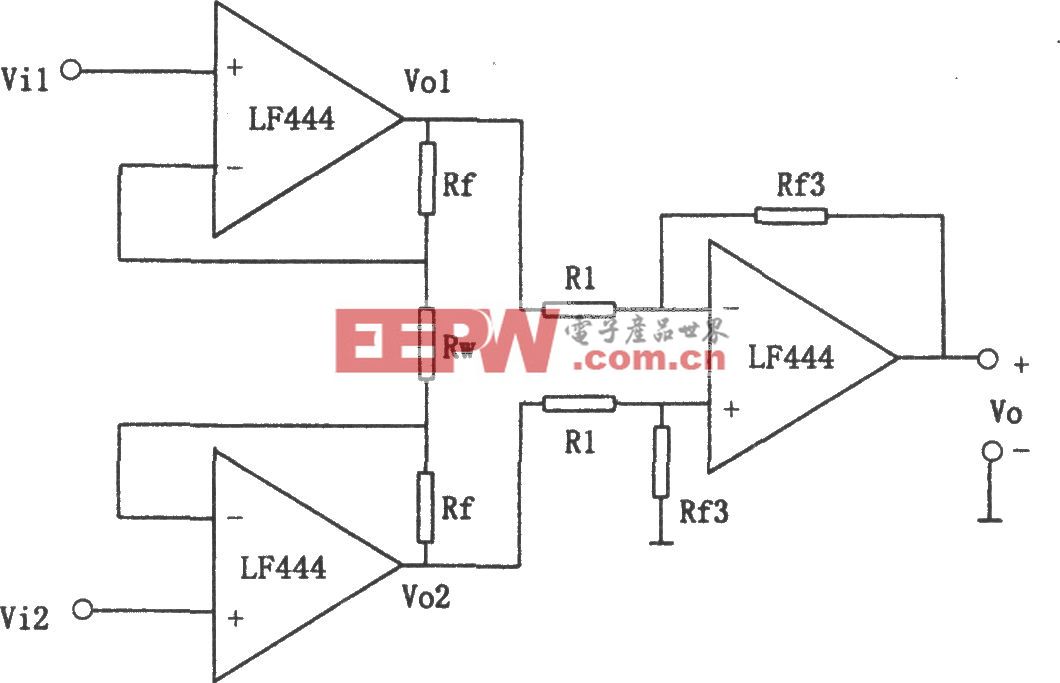

按照式(5)中CCOS各级联部分的关系,文献[4]中给出一种电路实现结构图,通过抽取使部分电路工作在更低频率。为了进一步提高滤波器设计的功耗使用效率,减小占用芯片的面积,对文献[4]的结构进行再次改进和优化。通过改变算法运算的具体步骤,来减少运算的步数,从而提高滤波器的效率。

首先把递归结构实现的部分改为非递归算法结构,降低功耗;

其次把CCOS滤波器的部分电路再次抽取降频,处理后每级表达式都可以与非递归算法结构的表达式合并,既可以使CCOS滤波器部分电路工作在低频降低功耗又可以大大减少存储单元数量。CCOS滤波器实现结构如图4(a)所示,图4(b)为对CCoS滤波器抽取改讲后整体改进型滤波器的结构。

评论