基于FPGA和IP Core的定制缓冲管理的实现

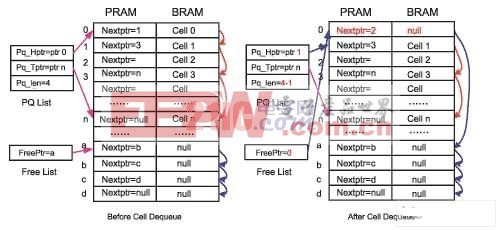

PQ List将尾指针n更新为新写入的地址a,同时更新PRAM中n地址的内容,将a作为下一跳添入n地址。基于节省操作周期,NULL的内容保留原值,不再更新。这样,一次BRAM的写入操作需要一次PRAM的读取操作及一次PRAM的写入操作。

QM模块接收调度模块的出队信息,将出队的PQ链表信息传送给BM模块进行读取操作。

图4 BM模块的写入操作

图5 读出操作的Free List堆栈结构

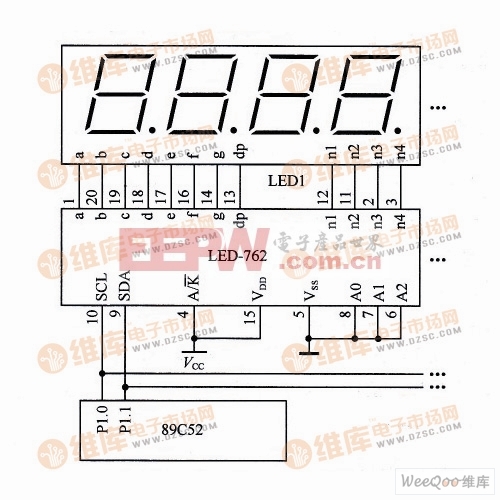

BM模块的读取操作由Read Control模块发起完成,当有数据单元需要读出,相应的数据单元地址则需要回收进入空闲地址队列Free List。对于不同的系统需求,空闲地址队列Free List有不同的形式。比较简单的操作是将Free List作为堆栈形式使用。

Read Control模块由PQ List的首地址0读出相应的BRAM中的内容,同时读出PRAM中对应的下一跳地址1,更新地址1为新的首地址。Free List将首指针a更新为刚释放的地址0,同时地址0中写入下一跳指针a。这样一次BRAM的读出操作需要一次PRAM的读取操作及一次PRAM的写入操作。

作为堆栈形式的空闲地址队列在实际操作中会把一部分空闲地址队列放入片内缓冲中。这样在读BRAM释放地址进入空闲地址队列时可以节省PRAM的一次写入操作,在写BRAM时申请空闲地址时可以节省PRAM的一拍读取操作。PRAM堆栈结构下内置空闲地址队列表如图6所示。

图6 PRAM堆栈结构下内置空闲地址队列表

评论