基于FPGA和IP Core的定制缓冲管理的实现

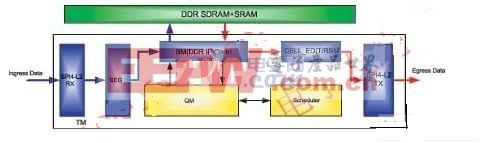

随着通信协议的发展及多样化,协议处理部分PE在硬件转发实现方面,普遍采用现有的商用芯片NP(Network Processor,网络处理器)来完成,流量管理部分需要根据系统的需要进行定制或采用商用芯片来完成。在很多情况下NP芯片、TM芯片、交换网芯片无法选用同一家厂商的芯片,这时定制TM成为了成本最低、系统最优化的方案,一般采用FPGA来实现,TM的常规结构如图1所示。

本文引用地址:https://www.eepw.com.cn/article/191494.htm

图1 TM的常规结构图

目前主流的TM接口均为SPI4-P2接口形式,SPI4-P2接口信号速率高,TCCS(Chan nel-to-channel skew,数据通道的抖动,包含时钟的抖动)难以控制,在常规情况下很难做到很高的速率。SPI4-P2接口为达到高速率同时避免TCCS问题在很多情况下都对接收端提出了DPA(动态相位调整)的要求。对于SPI4-P2接口形式可直接采用Altera公司的IP Core实现。Altera的主流FPGA均实现了硬件DPA功能,以Stratix II器件为例,在使能DPA的情况下使用SPI4-P2 IP Core可实现16Gb/s的接口数据速率。

SEG模块为数据切分块,根据交换网的数据结构要求,在上交换网的方向上负责把IP包或数据包切分为固定大小的数据块,方便后期的存储调度以及交换网的操作处理,SEG模块可配合使用SPI4-P2 IP Core来实现。与SEG模块对应的是RSM模块,RSM模块将从交换网下来的数据块重新组合成完整的IP包或数据包。

BM(Buffer Management)模块为缓冲管理模块,管理TM的缓冲单元,完成DRAM的存取操作。外部DRAM的控制部分可使用使用DDR SDRAM IP Core实现。

QM模块为队列管理模块,负责完成端口的数据队列管理功能,接收BM模块读写DRAM时的数据入队、出队请求,TM所能支持的数据流的数目、业务类型数目、端口的数目等性能指标在QM模块处体现出来。

Scheduler模块为调度模块,根据数据包类型及优先级和端口分配的带宽进行调度,TM流量整形、QOS等功能通过调度模块实现。

CELL_EDIT模块完成输出数据的封装,把由DRAM中读出的数据封装后发送出去。

在TM中需要基于数据服务策略对于不同服务等级的数据包进行不同的管理策略,同时要保证流媒体的数据包不能乱序,数据包有大有小,经过SEG模块所分割成的数据块的数目也有多有少,这样就必须有一套行之有效的数据结构基于链表的方法管理这些数据。QM模块基于业务、数据流的方式管理队列,包的管理便由BM模块完成。

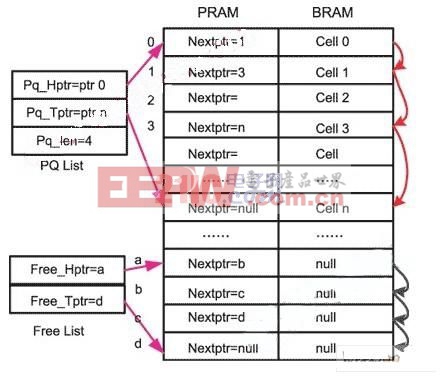

BM模块中基于包的数据结构方面由两部分构成:BRAM和PRAM。BRAM为数据缓冲区,对应片外的DRAM。BRAM负责存储数据单元,相对于SEG模块切分的数据单元,BRAM内有相应大小的存储单元BCELL与之对应,BCELL在BRAM内以地址空间划分,每个BCELL相同大小,BCELL为BRAM的最小存取单元。在实际系统中基于SEG模块切分的数据单元大小,BCELL一般为64~512B。

PRAM为指针缓冲区,PRAM对应片外的SSRAM。PRAM内部同样以地址空间分为PCELL,PCELL与BCELL一一对应,每一个PCELL对应于一个BCELL,对应的PCELL与BCELL地址相同。

PCELL的地址对应的代表相应单元的BCELL的地址,PCELL中的基本信息是下一跳指针。PRAM与BRAM关系如图2所示。

图2 PRAM与BRAM关系图

评论