如何实现FPGA到DDR3 SDRAM存储器的连接

采用90nm工艺制造的DDR3 SDRAM存储器架构支持总线速率为600 Mbps-1.6 Gbps (300-800 MHz)的高带宽,工作电压低至1.5V,因此功耗小,存储密度更可高达2Gbits。该架构无疑速度更快,容量更大,单位比特的功耗更低,但问题是如何实现DDR3 SDRAM DIMM与FPGA的接口呢?

本文引用地址:https://www.eepw.com.cn/article/191492.htm关键词——均衡!

如果没有将均衡功能直接设计到FPGA I/O架构中,那么任何设备连接到DDR3 SDRAM DIMM都将是复杂的,而且成本还高,需要大量的外部元器件,包括延时线和相关的控制。

什么是均衡?为什么如此重要?

为了在支持更高频率时提高信号完整性,JEDEC委员会定义了一个fly-by(飞越式)端接方案,该方案采用了时钟和命令/地址总线信号来改善信号完整性以支持更高的性能。当时钟和地址/命令通过DIMM时,fly-by拓扑结构通过故意引起每个DRAM上的时钟和数据/选通之间的飞行时间偏移(flight-time skew)来减小并发开关噪声(SNN),如图1所示。

飞行时间偏移可能高达0.8 tCK,当该偏移被扩展得足够宽时,将不知道数据在两个时钟周期中的哪个内返回。因此,均衡功能可以使控制器通过调节每个字节通道内的时序来补偿这一偏移。最新的FPGA能够为各种应用提供与双倍数据率SDRAM存储器接口的许多功能。但是,要与最新的DDR3 SDRAM一道使用,还需要更鲁棒的均衡方案。

FPGA I/O结构

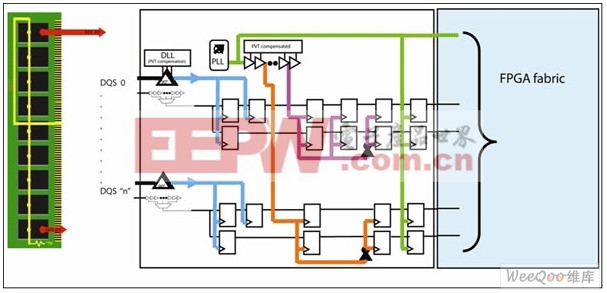

像Altera Stratix III系列高性能FPGA提供的I/O速度高达400 MHz (800 Mbps),还具有很高的灵活性,能够支持现有的和新兴的外部存储器标准,如DDR3。

图1:DDR3 SDRAM DIMM:飞行时间偏移降低了SSN,数据必须被控制器调高到两个时钟周期。

读均衡

在读取操作中,存储器控制器必须补偿由飞越存储器拓扑引起的、影响读取周期的延时。均衡可以被视作为出现在数据通道上的比I/O本身延时还要大的延时。每个DQS都要求一个同步时钟位置的独立相移(经过了工艺、电压和温度(PVT)补偿)。图2显示出同一读取命令下从DIMM返回的两个DQS组。

图2:I/O单元中的1T、下降沿和均衡寄存器。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论