基于FPGA和DDS技术的任意波形发生器设计

摘要:根据现代电子系统对信号源的频率稳定度、准确度及分辨率越来越高的要求,结合直接数字式频率合成器(DDS)的优点,利用FPGA芯片的可编程性和实现方案易改动的特点,提出了一种基于FPGA和DDS技术的任意波形发生器设计方案。采用VHDL和原理图输入方式,在Quar-tusⅡ平台下实现该设计的综合和仿真,用Matlab对仿真数据进行处理及显示,验证了设计的正确性。通过设置参数可以灵活控制输出频率和分辨率。

关键词:DDS;FPGA;波形发生器;VHDL

0 引言

随着现代电子技术的发展,在通讯、雷达、宇航、电视广播、遥控遥测和电子测量等使用领域,对信号源的频率稳定度、频谱纯度、范围和输出频率提出了越来越高的要求。为了提高频率稳定度,经常采用晶体振荡器等方法来解决,但已不能满足众多应用场合的要求。伴随电子测量技能与计算机技能的紧密结合,一种新的信号发生器——任意波形发生器应运而生,它可产生由用户定义的任意复杂的波形,因而具有广阔的运用发展前景。目前设计波形发生器的要领通常有三种:

(1)传统的直接频率合成技能(DS)。该类要领能实现高速频率变换,具有低相位噪声以及所有要领中最高的工作频率。但由于采用大量的倍频、分频、混频和滤波环节,导致其结构复杂、体积庞大、成本昂贵,而且容易产生过多的杂散分量。

(2)锁相环式频率合成器(PLL)。该类技能具有良好窄带跟踪特征,可选择所需频率信号,抑制杂散分量,且省去大量滤波器,有利于集成化和小型化。但由于锁相环本身是个惰性环节,锁定时间较长,因而频率转换时间较长,且由模拟要领合成的正弦波参数(如幅度、频率和相位等)都难以定量控制。

(3)直接数字式频率合成器(direct digital frequency,DDS)。该类要领具有高频率稳定度、高频率分辨率以及极短的频率转换时间。此外,全数字化结构便于集成,输出相位连续,频率、相位和幅度均可实现程控,而且理论上能够实现任意波形。

鉴于DDS技术的优点,本文利用FPGA芯片的可编程性和实现方案易改动的特点,提出一种基于FPGA和DDS技术的任意波形发生器设计新方法。

1 DDS的基本原理

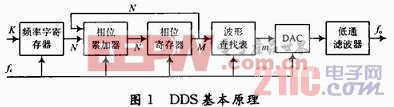

DDS的基本原理是利用采样定理,通过查表法产生波形。DDS的结构有很多种,其基本的电路原理可用图1来表示。

DDS是从相位概念出发,直接对参考正弦信号进行抽样,得到不同的相位,通过数字计算技术产生对应的电压幅度,最后滤波平滑输出所需频率。下面通过从相位出发的正弦函数产生描述DDS的概念。

图1中,K为频率控制字;N为相位累加器的字长;M为ROM地址线位数;m为ROM数据线位数,即DAC的位数;fc为DDS系统的参考时钟源,通常是一个具有高稳定性的晶体振荡器,为整个系统的各个组成部分提供同步时钟。

DDS的数学模型可归结为:在每一个时钟周期T内,频率控制字K与N比特相位累加器累加1次,同时对2N取模运算,得到的和(以N位二进制数表示)作为相位值,以二进制代码的形式查询正弦函数表ROM,再将相位信息转变成相应的数字量化正弦幅度值。ROM输出的数字正弦波序列经数/模转换器转变为阶梯模拟信号,最后通过低通滤波器平滑后得到一个纯净的正弦模拟信号,其频率为:![]()

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fc,加法器将频率控制字K与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加1次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

评论