基于FPGA和DDS技术的任意波形发生器设计

2.1 DDS模块的基本结构设计

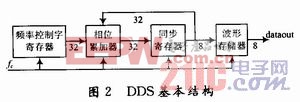

整个DDS系统的设计采用层次结构,采用VHDL与原理图输入相结合的方法,DDS基本结构如图2所示。

下面就各个部分的设计分别介绍:该设计中采用的频率字为32位,即N=32,RAM为256×8位,故ROM的地址线宽M=8,输出数据线宽L=8。由于RAM地址线为8位(28=256),而相位累加器的输出为32位,为了保证它们之间的对应,将相位累加器的高8位与RAM的地址线相连。这样存在多个相位地址对应同一个RAM地址的情况,如果把相位累加器输出的所有位数全部用来查询RAM,那么RAM的容量会非常的大,如此巨大的RAM表容量在实际工作中难以实现。因此,常使用相位地址高位来寻址,舍去低位的相位截断方法。当然,这种方法会引入一定的噪声,但

对于节省的资源来说,这种方法还是值得的。

2.2 DDS模块的总体设计

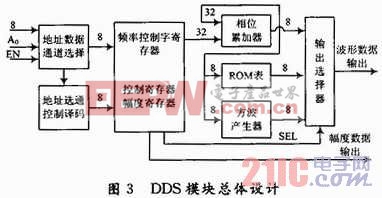

该设计主要由接口部件、频率及控制部件、相位累加器、波形数据产生部件和输出选择器组成,如图3所示。

接口部件主要完成接收单片机发送过来的频率参数及控制参数其中A0为数据通道和地址通道选择位,EN为数据写入使能。频率及控制部件主要完成频率控制字及输出控制参数的存储,由5个带写使能的8位同步寄存器组成。相位累加器为DDS主要部件实现相位的累加。波形数据产生部件的功能是将相位数据转化为所需的波形数据,其中正弦波和三角波数据由查ROM表获得,锯齿波数据直接由相位累加器输出得到,方波数据是相位累加器输出数据与设定数据比较获得。输出选择器的SEL端接到控制参数寄存器,它的4个数值分别选择4种不同的波形输出。

3 DDS仿真实验结果

设置输出100 kHz正弦波,由式,得,通过计算K=21 477 072=147B6DOH,按照此数据设置好频率控制寄存器的参数,其仿真波形如图4、图5所示。

评论