第二代串行 RapidIO 和低成本、低功耗的 FPGA

随着诸如无线、有线和医疗/图像处理应用的带宽需求不断提高,设计师们必须依赖必要的工具集来获得其所需的实时信号处理功能。在无线领域,例如现有的3G 网络覆盖,如HSPA+和EV-DO(即3G+)以及现在新兴的4G部署,主要的关注焦点在于数据吞吐量和回传的要求。它们要能够支持迅速增长的用户群,以及使用这些技术实现的无数视频和数据应用。因此就需要高速处理能力,以及同样重要的高度可靠、高吞吐量和低延迟的接口协议,来支持这些应用中所必需的各种DSP(DSP farm)、协同处理和桥接应用的需要。并且与大多数系统相同,成本和功耗也同样非常重要。DSP和网络处理单元(NPU)器件,加上支持第二代串行RapidIO(SRIO)的低成本、低功耗FPGA,可以为满足这些挑战提供一个理想的平台。

本文引用地址:https://www.eepw.com.cn/article/191218.htm第二代SRIO

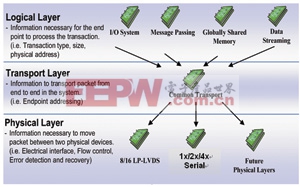

RapidIO规范是为各种终端定义的一种基于分组的技术,它最初是用于连接其他终端的数据包和交换的处理。如图1所示,该协议栈是一个三层协议规范,分为物理层协议、数据包传输(路由)层协议,以及逻辑层中的多种传输类型。

图1 RapidIO协议栈

总体来看,第二代规范主要增加了对5/6Gb/s串行数据速率(SERDES)和用于高速串行通道的2x线路配置(与之前v1.3版本规范中仅支持1x/4x相比)的支持。正如前文所述,重点是在不牺牲设计的成本或功耗预算的情况下,提高性能,因此本文的重点在于介绍第二代规范的2x功能。这是一个关键的增强功能,因为在许多情况下,系统需要比一条3.125Gb/s线路提供更大的吞吐量,但是使用4x 线路配置又显得多余了。这就是现在2x SERDES 线路配置可以提供的一个有效解决方案,让设计人员选择仍然使用一个低成本、低功耗的FPGA解决方案,例如Lattice ECP3,并且还能支持大多数的应用高达4x的线路配置,速率高达3.125Gb/s。

FPGA的可编程性和灵活性在逻辑层发挥了很大的作用,可以实现多种通信技术。如图1所示,有4种数据传输协议。它们是直接I/O访问、消息传递、GSM和数据流。逻辑层可以进行定制,这取决于系统架构/要求,以确定SRIO终端如何进行数据交换。图1显示了RapidIO规范表示的协议栈。

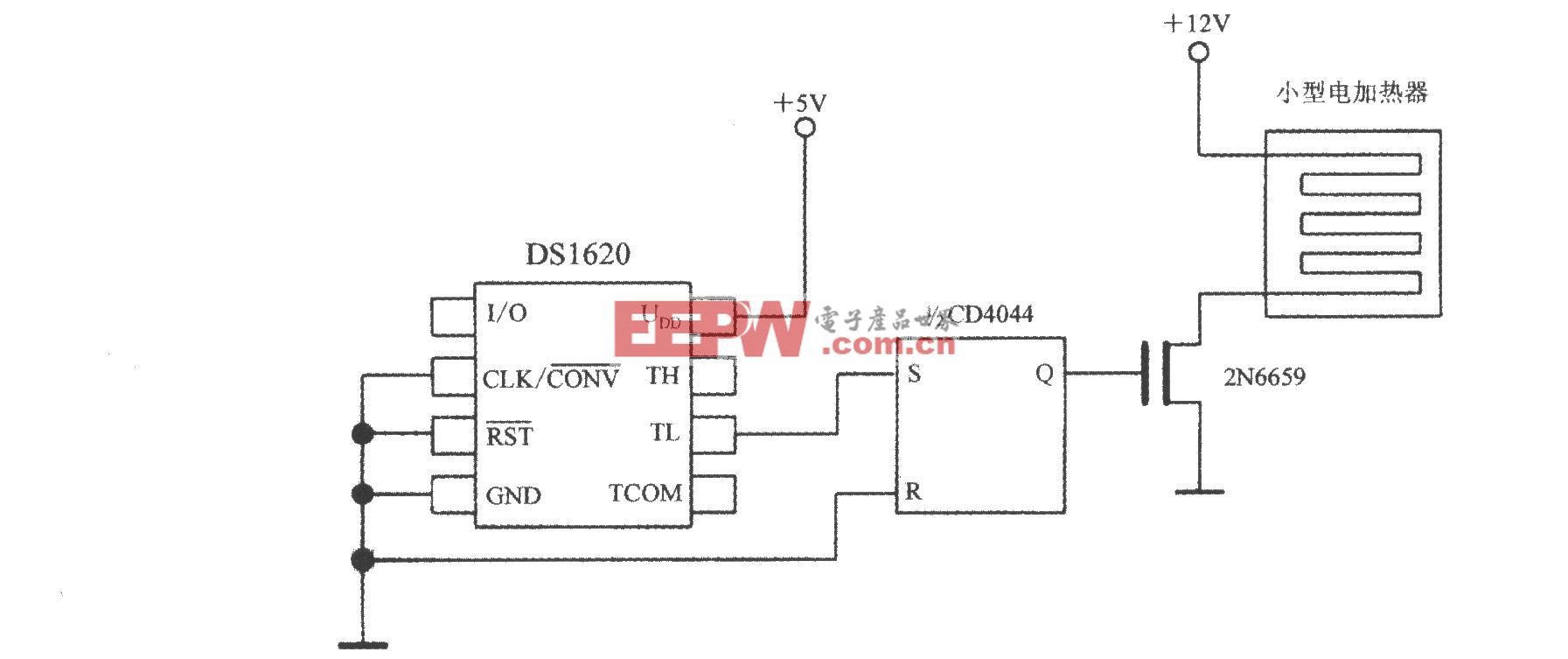

图2显示了如何使用低成本的可编程平台来实现协议栈。物理层和传输层使用标准的软IP核实现,但逻辑层还剩下许多可供用户定制的特性,以满足特定的设计要求。

图2 FPGA实现示例

评论