优化FIR数字滤波器的FPGA实现

摘要:基于提高速度和减少面积的理念,对传统的FIR数字滤波器进行改良。考虑到FPGA的实现特点,研究并设计了采用Radix-2的Booth算法乘法器以及结合了CSA加法器和树型结构的快速加法器,并成功应用于FIR数字滤波器的设计中。滤波器的系数由Matlab设计产生。仿真和综合结果表明,Booth算法乘法器和CSA算法加法器树,在满足FIR数字滤波器的性能要求的同时,在电路实现面积上、尤其是速度上有明显的优化;并且当数据量越多时,优化也越明显。

关键词:Matlab;Booth算法;CSA算法;ISE

研究数字滤波器的意义就在于它们正日益成为一种主要的DSP(DigitaI Signal Processing)运算,并正在逐渐代替传统的模拟滤波器。它可以保证任意幅频特性的同时具有严格的线性相频特性。而现场可编程门阵列(Field Programmable Gate Array,FPGA)可并行执行的特点决定它更加广泛地应用于实时数字信号处理领域。不能想象今天的生活如果没有音频;视频和言语交际的样子,而这些都要应用数字信号处理技术。并且在任何时候,高性能,低规模,低成本都是设计的目标。滤波器(Finite Impulse Response,FIR)的实现方法有很多种,最常见的有串行结构和并行结构方法。前者根据FIR滤波器的实现表达式,将滤波器实质看作是做一个乘累加运算。一次乘累加运算的次数由滤波器的阶数来决定。这种方法使用硬件资源相对较少,但速度较慢。并行结构的方法,将滤波器的串行实现展开,就可以直接用多个乘法器和加法器并行实现,其可以在一个时钟周期内完成一次滤波,但要占用大量的乘累加器,器件延迟比较大。目前为了满足面积和速度的需要,人们通常采用Booth算法、CSD算法,分布式算法等技术对FIR设计进行优化,优化效果各有利弊。本文针对串行结构对乘累加运算的乘和加分

别进行优化设计。分析了提高乘法器速度的途径;针对多数据量的运算,提出了一种新型的快速加法器的解决方案。体现了优化设计中提高速度和减小面积的设计理念。同时给出并实现了一个16阶FIR的设计实例。

1 用Matlab设计滤波器系数

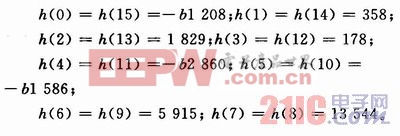

利用Matlab软件的FDATool模块,选择滤波器类型为低通FIR,设计方法为窗口法,阶数为16,窗口类型为Kaiser,数据采样频率fs为4.8 kHz,滤波器的截止频率fc为1.08 kHz,导出的滤波器系数为16个15位的小数。将每一个系数扩大相同的倍数,最后四舍五人得到一系列整数系数。如下:

2 优化FIR滤波器在FPGA中的实现结构

2.1 FIR滤波器的基本算法原理

本文采用滤波器实现的基本的串行乘累加结构。FIR滤波器的差分方程可表示为:

![]()

式中:t为滤波器的阶数。

其直接运算结构如图1所示。

从公式(1)中可知FIR滤波器在硬件上的设计主要是完成乘累加功能,实现的一种方法是直接相乘累加。在实际应用中,当滤波器设计对滤波速度要求不高时,可采用串行结构或改进串行结构来实现,这样可以选取资源较少的器件,降低设计成本;当对滤波速度有较高要求时,可以考虑采用并行或DA来实现。但要进行FIR运算,尤其在阶数较高时,几乎无法在FPGA内实现并行结构,所以这里采用串行运算的结构,仅使用一个乘加器。所以本文的设计着重于提高串行结构FIR的速度。下面将介绍一种高速的Booth算法乘法器和高速的加法器。

评论