第二代串行 RapidIO 和低成本、低功耗的 FPGA

低成本、低功耗拥有SRIO功能的FPGA的作用和优势

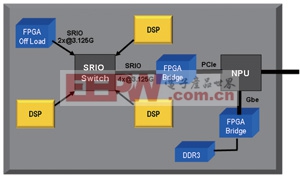

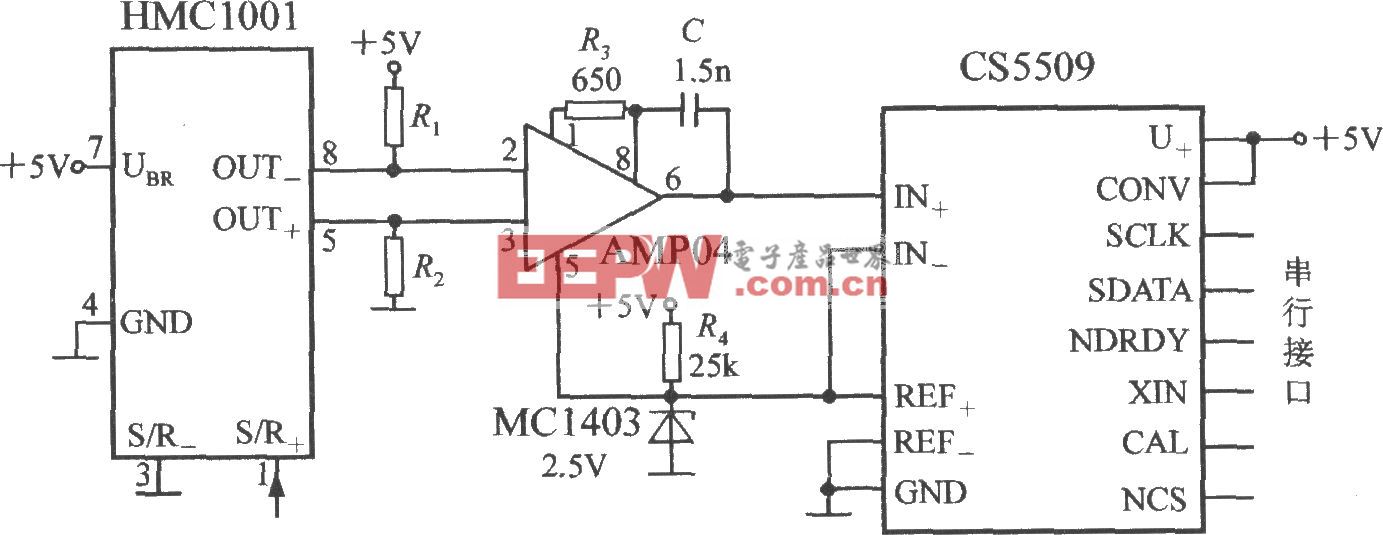

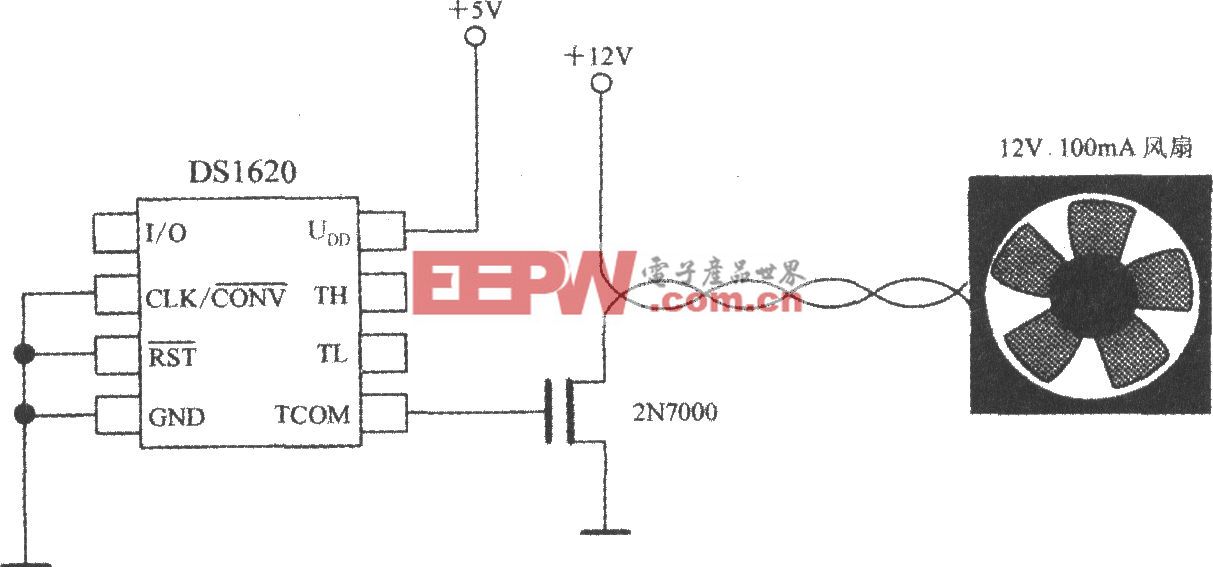

如上所述,许多处理都由于DSP和NPU而失败,而通常情况下,它们两者的分工不同。DSP应用,尽管也进行密集型处理,但往往需要更多的中断驱动(如门铃),因为它们是在处理阵列中实现的,或者要接口到一个SRIO开关或终端——可能甚至要提供从SRIO到另一个基于SERDES的协议,如GbE或PCIe的桥接机制。而NPU更多地扮演了一个警察的角色来进行数据处理,主要负责通信量和队列处理。如图3中的示例所示,说明了低成本、低功耗FPGA可以如何协助实现一个成功且有效的系统解决方案。

图3 FPGA应用示例

FPGA因其固有的灵活性和快速的产品上市时间的优势,超越了ASIC而长期受到市场欢迎,但是最近,这些优势只能通过使用高级的高端器件才能实现,这就提高了成本和功耗预算。之前,低成本、低功耗FPGA仅限于“接口逻辑”和“错误修正”应用。然而,随着FPGA的价值定位大大地扩展,现在已不再是如此。为了支持处理需求,保持严格的成本和功耗预算,FPGA的架构已经经历了发展变化,显著地提高了性能、特性和逻辑密度,并且以比传统FPGA更低的功耗和价格来实现。增强的功能,如集成的SERDES、高速嵌入式DSP块、DDR3存储器支持和嵌入式存储器功能,已成为处理设计中的关键组成部分。系统工程师和设计工程师现在能够利用这些可编程平台实现复杂的信号路径应用,支持RRH和基带处理功能,以及有线和图像处理应用,并且与传统、高端的带有SERDES功能的FPGA产品相比,具有更低的功耗和成本。

小结

系统设计人员将继续面临设计更高性能系统并同时保持较低的系统构建和运营成本的压力。而这种压力还将继续延续下去。

过去,FPGA在系统设计中发挥了重要作用,但现在还需要新的性能,同时需要降低整个系统的构建和运营成本。功能丰富、低成本的FPGA实现了快速的产品上市时间与较短的投资回报周期,并且拥有能够适应不断发展的标准的灵活性和性能。系统/设计工程师现在还拥有了一个令人兴奋的、改进的工具集来解决不断演进的信号处理市场的挑战。

评论