一种基于FPGA的雷达数字信号处理机设计与实现

摘要:结合具体的雷达导引头型号项目.从数字信号处理机的原理出发,根据项目的要求提出了一种基于DBF技术的某型导引头信号处理机设计方案,方案以Xilinx公司Virtex4 SX55 FPGA作为数字信号处理的核心器件,实现对6阵元阵列天线接收的回波信号进行实时采集和处理。对系统硬件和软件总体设计及基频信号产生模块、回波信号采集模块、控制信号产生模块和时钟电路模块的具体设计进行了详细介绍。最后在暗室环境对系统进行了测试,测试结果表明系统达到了设计要求。

关键词:数字信号处理机;FPGA;DBF;基频信号;回波信号

0 引言

导弹主要依靠制导系统进行制导,完成从发射到命中目标的全过程。制导系统一般利用地面制导雷达或弹载导引头对目标进行探测、参数计算、控制指令形成与传输、程序控制和伺服控制等。雷达导引头是建立在雷达、自动控制、制导、微型计算机、精密机械、微电子、小型化和可靠性能多项专门技术基础上的一种复杂制导设备。各国尤其是先进国家都十分重视雷达导引头的研制及其相关技术的研究,从而将智能化、高命中率、高摧毁概率的导弹武器的研制应用推向新阶段。

本文采用脉冲多普勒、数字波束形成等技术,为某型雷达导引头信号项目设计了其关键部分——雷达数字信号处理机。本处理器采用FP GA平台实现,文中详细介绍了该处理器基于FPGA的基频信号产生模块、回波信号采集模块、控制信号产生模块和时钟模块等硬件模块的设计思路。

1 系统方案设计

目前,主要采用三种方法实现雷达数字信号处理系统设计:基于DSP技术实现雷达数字信号处理,基于“FPGA+DSP”技术实现和基于FPG A技术来实现。本方案选用Xilinx Virtex4 FPGA XC4VSX55,其属于Xilinx SX系列,专用于高速数字信号处理领域,FPGA非常适合于高速数据的采集控制、高速数据传输控制,且目前的主流FPGA均含有硬件乘加器、大量的逻辑单元、流水线处理技术等硬件结构,可高速完成FFT、FIR、复数乘加、卷积、三角函数以及矩阵运算等数字信号处理。高端FPGA更是含有大量的DSP单元、RAM单元、MGT高速传输单元、DDRII数据控制器等IP核,这些均是实现高速实时数字处理的重要资源。此外,FPGA编程灵活,易于升级。其高度集成性和高灵活性使对外部硬件的需要更少,额外的硬件开销大大减小,非常适用于雷达数字信号的处理和将来的算法升级。因此本方案采用FPGA技术进行雷达信号的处理。

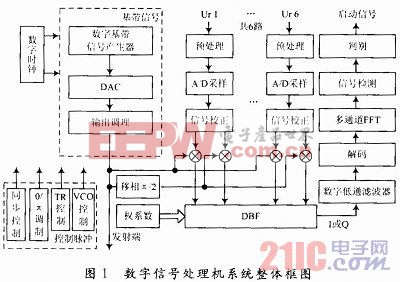

根据项目的设计需求,设计的雷达数字信号处理机系统整体框图如图1所示。

输入调理电路对接收到的回波信号进行预处理,预处理过后的信号经ADC转换为数字信号;采样后的信号经频率搬移,将100MHz的中频信号搬移到20MHz,然后对6个通道的信号进行幅度校正,消除通道间的不平衡问题。校正后的6路信号分别与两个正交本振信号相乘,进行数字混频,完成信号的正交分解,得到12路I/Q正交信号。12路I/Q信号与预先设置的权值进行加权计算并进行累加,完成数字波束形成(DBF),得到一路合成信号;通过FIR低通滤波器,对数字波束合成后的信号进行数字滤波,滤除30 MHz以上的谐波信号;由于发射信号采用了伪码调相技术,所以对DBF后的信号依照发射信号的m序列进行伪码解调(即对回波信号进行相位变换),完成回波信号的解码。对滤波后的信号进行相参累积,累积次数达到设定值后,进行FFT变换;FFT结果与检测门限进行比较,当发现回波信号特征时,给出回波的通道号和频率,并给出启动信号。

评论