一种基于FPGA的雷达数字信号处理机设计与实现

2.2 软件设计

本文设计的雷达数字信号处理机的软件没汁主要分为FPGA程序设计、系统驱动设计和用户软件设计三个部分。FPGA程序是系统算法的核心,完成ADC的控制以及DBF算法等;系统驱动设计和用户软件设计主要完成系统的人机交互功能,不是本文讨论的重点,此处只讨论FPGA程序的设计。

FPGA程序主要完成信号处理算法。该程序利用Xilinx公司提供的System Generator工具,对数字信号处理的过程进行建模和设计。Syst em Generator适于利用FPGA设计高性能数字信号处理系统。它利用业内最先进的FPGA开发高度并行系统提供系统建模和从Simulink与Matlab自动生成代码的功能,System Generator整合了DSP系统的RTL、嵌入式、IP、Matlab和硬件元件DSP建模。它利用包含信号处理(如FIR滤波器、FFT)、纠错(如Viterbi解码器、ReedSolomon编码器/解码器)、算法、存储器(如FIFO,RAM,ROM)及数字逻辑功能的Xilinx模块集,在Simulink内构建和调试高性能DSP系统。Xilinx模块集提供的模块可以使用户导入Matlab功能(如创建控制电路)及HDL模块,迅速完成复杂的数字信号处理算法设计。

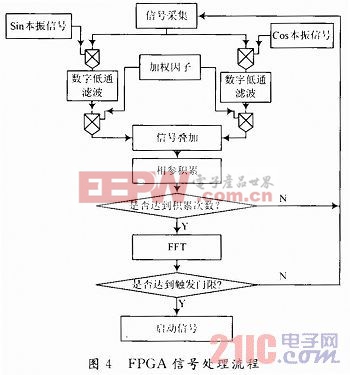

一路回波信号经A/D采集后的数字序列分别与两个正交本振信号进行相乘,完成正交变换,得到两路I/Q信号。然后,通过数字低通滤波器实现数字混频。本设计在这里选择正弦和余弦两个信号作为正交变换的本振信号,无论从数学运算上,还是具体实现上都能确保其正交性。设计中采用的是6单元均匀线阵天线,因此共得到12路I/Q信号。12路I/Q信号与加权因子相乘后进行数字波束合成,得到两路I/Q信号,然后进行信号叠加。叠加后的信号进行相参积累,当积累次数达到设置值时,进行FFT处理;否则,继续信号采集过程。将FFT处理的结果和设置的门限相比较,如超过门限时,触动启动信号;否则,继续信号采集过程。FPGA处理的流程如图4所示。本文引用地址:http://www.eepw.com.cn/article/190578.htm

3 系统测试

在实际条件下,对数字信号处理机中的DBF系统合成波束的天线方向图进行了测试,以检验是否和理想条件下的天线方向网一致。具体步骤如下:

(1)测试环境:某研究所暗室。

(2)测试条件:6元15 mm接收天线成均匀直线阵排列、1元发射天线、雷达数字信号处理电路板、转台以及其他必要设备。

(3)测试方法:将6元接收天线放置在转台的0°刻度所在的直线上,测试的信号源放在转台前方,并在90°刻度的延长线上。此时设定阵列天线所在的直线为x轴,法线方向为y轴,转台中心为坐标零点。转动转台,使信号源与天线的夹角分别为90°,60°,20°,调整阵列天线权值,使主瓣方向指向信号源方向。调整完成后,测量并记录三种情况下的天线方向图。

(4)测试结果:根据实测数据绘制的三种情况下的阵列天线方向图如图5~图7所示。

评论