Altera Cyclone IV GX系列FPGA开发方案

Altera 公司的Cyclone IV 系列FPGA包括两个系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元,高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供高达八个3.125 Gbps高速收发器,用于大批量,成本敏感的应用如无线、有线、广播、工业,用户以及通信等行业.本文介绍了Cyclone IV 器件系列主要特性,收发器通道框图以及Cyclone IV GX FPGA开发套件主要特性,框图,电路图和材料清单.

本文引用地址:https://www.eepw.com.cn/article/190523.htmAltera 新的Cyclonereg;IV 系列 FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型

号:

■ Cyclone IV E— 最低的功耗,通过最低的成本实现较高的功能性

■ Cyclone IV GX— 最低的功耗,集成了3.125 Gbps 收发器的最低成本的FPGA

Cyclone IV 器件集成了一个可选择的低成本收发器,在未影响性能的情况下,节省了功耗及成本。针对无线、有线、广播、工业,用户以及通信等行业中的低成本的小型应用,Cyclone IV 器件无疑是最理想的选择。

Cyclone IV 器件系列主要特性:

■ 低成本、低功耗的FPGA 架构:

■ 6 K 到150 K 的逻辑单元

■ 高达6.3 Mb 的嵌入式存储器

■ 高达360 个18 × 18 乘法器,实现DSP 处理密集型应用

■ 协议桥接应用,实现小于1.5 W 的总功耗

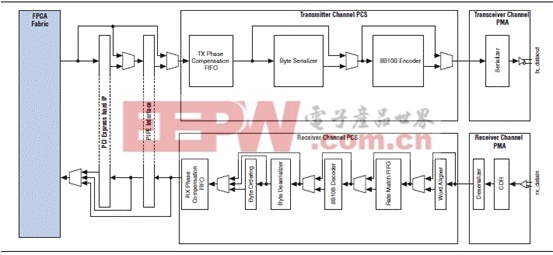

■ Cyclone IV GX 器件提供高达八个高速收发器以支持:

■ 高达3.125 Gbps 的数据速率

■ 8B/10B 编码器/ 解码器

■ 8-bit 或者10-bit 位物理介质附加子层(PMA) 到物理编码子层(PCS) 接口

■ 字节串化器/ 解串器(SERDES)

■ 字对齐器

■ 速率匹配FIFO

■ 公共无线电接口(CPRI) 的TX 位滑块

■ 电路空闲

■ 动态通道重配置以实现数据速率及协议的即时修改

■ 静态均衡及预加重以实现最佳的信号完整性

■ 每通道150 mW 的功耗

■ 灵活的时钟结构以支持单一收发器模块中的多种协议

■ Cyclone IV GX 器件对PCI Express (PIPE)(PCIe)Gen 1 提供了专用的硬核IP:

■ ×1,×2, 和×4 通道配置

■ 终点和根端口配置

■ 高达256-byte 的有效负载

■ 一个虚拟通道

■ 2 KB 重试缓存

■ 4 KB 接收(Rx) 缓存

■ Cyclone IV GX 器件提供多种协议支持:

■ PCIe (PIPE) Gen 1×1,×2, 和×4 (2.5 Gbps)

■ 千兆以太网(1.25 Gbps)

■ CPRI ( 高达3.072 Gbps)

■ XAUI (3.125 Gbps)

■ 三倍速率串行数字接口(SDI)( 高达2.97 Gbps)

■ 串行RapidIO(3.125 Gbps)

■ Basic 模式( 高达3.125 Gbps)

■ V-by-One( 高达3.0 Gbps)

■ DisplayPort(2.7 Gbps)

■ 串行高级技术附件(Serial Advanced Technology Attachment (SATA))( 高达3.0 Gbps)

■ OBSAI( 高达3.072 Gbps)

■ 高达532 个用户I/O

■ 高达840 Mbps 发送器(Tx), 875 Mbps Rx 的LVDS 接口

■ 支持高达200 MHz 的DDR2 SDRAM 接口

■ 支持高达167 MHz 的QDRII SRAM 和DDR SDRAM

■ 每器件中高达8 个锁相环(PLLs)

■ 支持商业与工业温度等级

Cyclone IV 器件系列体系结构

这一部分介绍了Cyclone IV 器件的体系结构,其中包括以下几方面内容:

■ FPGA 核心架构

■ I/O 特性

■ 时钟管理

■ 外部存储器接口

■ 配置

■ 高速收发器( 仅适用于Cyclone IV GX 器件)

■ PCI Express 的硬核IP( 仅适用于Cyclone IV GX 器件)

FPGA 核心架构

Cyclone IV 器件采用了与成功的Cyclone 系列器件相同的核心架构。这一架构包括由四输入查找表(LUTs) 构成的LE, 存储器模块以及乘法器。

每一个Cyclone IV 器件的M9K 存储器模块都具有9 Kbit 的嵌入式SRAM 存储器。您可以把M9K 模块配置成单端口、简单双端口、真双端口RAM 以及FIFO 缓冲器或者ROM,通过配置也可以实现表1-7 中的数据宽度。

Cyclone IV 器件中的乘法器体系结构与现有的Cyclone 系列器件是相同的。嵌入式乘法器模块可以在单一模块中实现一个18 × 18 或两个 9 × 9 乘法器。Altera 针对乘法器模块的使用提供了一整套的DSP IP,其中包括有限脉冲响应(FIR), 快速傅里叶变换(FFT) 和数字控制震荡器(NCO) 功能。Quartusreg;II 设计软件中的DSP Builder 工具集成了MathWorks Simulink 与MATLAB 设计环境,从而实现了一体化的DSP 设计流程。

图1.Cyclone IV GX 器件的收发器通道框图

评论