SPI IP核及其在微投影系统中的应用

摘要:介绍了SPI总线控制器IP核的硬件结构与应用方法,并着重介绍了该IP核在微投影系统中的使用,以完成微显示芯片的初始化。实验表明,该SPI总线接口使用灵活,便于移植,并且稳定可靠。

关键词:SPI总线控制器;Nios II处理器;IP核;可编程片上系统;微投影

引言

SPI总线作为一种简单高效的4线串行传输总线,在电子器件和系统中应用非常普遍,由于其输入和输出的信号线彼此独立,因而传输可靠性更好。Altera公司的EDA设计工具中有自带的SPI总线控制IP核,但目前介绍该IP核具体应用的文献不多,本文结合我们在微投影系统研究中的需求,给出了该SPI IP核的应用实例。

1 SPI核的工作原理

1.1 硬件结构

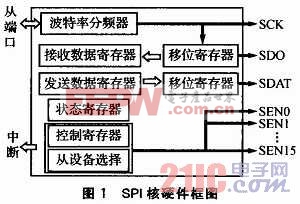

SPI核的硬件结构如图1所示,主要由波特率分频器、发送数据寄存器、接收数据寄存器、状态寄存器和控制寄存器组成。波特率分频器主要将Avalon的系统时钟进行分频,SCK可以配置的频率=Avalon系统时钟频率/(2的倍数)。

该IP核可以配置为主和从两种模式。本设计为嵌入在FPGA中SPI核为主工作模式,可以控制最多16个从设备,如图1所示的SEN0~SENl5。只有一个器件时,默认为SEN0信号。SPI核传输的数据宽度是由用户配置的,可在1~32位之间,当一次数据传输结束之后SPI核发出一个中断请求。

主要实现两种传输逻辑(以主模式为例):

①发送逻辑。待发送的数据由Avalon从端口送入发送数据寄存器,再移入移位寄存器中,SCK跳变沿到来时开始数据传输(经SDAT信号线发出,先移入的数据是高位还是低位,取决于SOPC Builder的配置)。

②接收逻辑。移位寄存器捕获到完整的数据后,再将其移入接收数据寄存器中(由SDO信号线捕获数据)。

1.2 软件结构

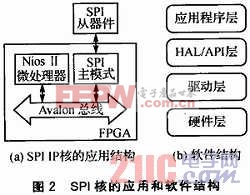

目前,在采用32位的软核Nios II处理器中,提供了4层软件开发模式:Nios II系统硬件,驱动程序层,硬件抽象层应用程序接口(HAL API),应用程序层。SPI核的应用和软件结构如图2所示。

评论