基于ARM和FPGA的声纳波形产生系统设

1、引言

本文引用地址:https://www.eepw.com.cn/article/152568.htm最佳声纳系统的设计需要从声纳波形、声纳信道和声纳接收机三方面进行综合考虑[1]。在声纳信道一定的假设下,需要设计最佳声纳波形和最佳接收机,使声纳系统能在给定的声纳环境中对目标有最佳的检测效果。工作在浅水中的主动声纳,其性能主要受限于混响级。根据波形选择与信道匹配的原则,针对混响信道,所选的声纳波形应使其模糊度函数尽量与混响信道散射函数不重合,而与声传输信号散射函数尽量重合[2]。基于这样的原则,常用的声纳信号单频信号(CW)、线性调频信号(LFM)抑制混响的能力比较如下:在检测静止或低速目标时,LFM和短CW较长CW有更好的混响抑制能力,但短CW波只适合近距离目标;在检测高速运动目标时,长CW脉冲是最合适的信号形式[2]。由此可见,主动声纳要完成目标捕获、识别、跟踪等不同任务,需要发射不同的声纳波形。同时针对远距离、低速和高速运动等目标的不同情况,也需要灵活的选择声纳波形。正是基于这样一种需求,本文把具有强大控制能力的微处理器ARM与具有灵活波形产生能力的直接数字频率合成技术(DDS)结合起来,用FPGA实现DDS技术,设计出了基于ARM和FPGA的声纳波形产生系统。

2、DDS基本原理

随着微电子技术的迅速发展,具有频率切换时间短、频率分辨率高、相位变化连续、易实现信号的多种调制等诸多优点的DDS技术,有了广阔的应用前景。DDS技术可以理解为数字信号处理中信号综合的硬件实现问题,即给定信号幅度、频率、相位等参数,产生所需要的信号波形。

DDS的基本结构包括:相位累加器、相位-幅值转换电路、数模转换电路及低通滤波器等。相位-幅值转换电路根据转换方式的不同可分为两大类[4]:(1)ROM查找表法。ROM中存储有不同相位对应的幅度值,可根据相位累加器输出的相位值寻址ROM,输出对应的幅值序列。 (2)计算法。对相位累加器输出的相位值,通过数学计算的方法得到对应的幅值。常用的实时计算方法有泰勒级数求值法、反函数求值法、CORDIC算法等。

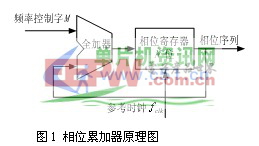

相位累加器是DDS电路中核心的模块,在工程实践上一般用数字全加器和数字寄存器的组合来实现,是一个典型的反馈电路。如图1所示。

其中, 为频率控制字, 为相位累加器的位数,fclk为系统参考时钟。相位累加器的工作过程为:每来一个参考时钟脉冲,频率控制字 与相位寄存器输出的相位数据累加一次,累加后的相位一方面反馈到全加器的输入端,以使全加器在下一时钟的作用下继续与频率控制字 相加;另一方面作为采样地址值送入ROM查找表。如此循环,当相位累加器累加满量后,就会产生一次溢出,ROM存储器的地址正好循环一次,完成一个周期性的动作,这个周期就是DDS合成信号的周期,累加器的溢出频率就是合成信号的频率[8]。图2为相位累加过程示意图及对应输出的占空比1:1的CW波。

评论