- 目录 第一节 | 摘要 P3 第二节 | DC-SCM是什么? P3 第三节 | 为什么要使用DC-SCM? P3 第四节 | DC-SCM架构 P4 第五节 | D

- 关键字:

FPGA DC-SCM

- 市调最新统计指出,大陆智能手机系统单芯片(SoC)4月整体出货量月减21.6%至1,760万套,其中联发科及高通(Qualcomm)等手机芯片供货商出货皆同步月减双位数,当中仅苹果小幅月减2.2%,显示新冠肺炎疫情封城及消费力道下滑,影响手机芯片市场需求。CINNO Research针对大陆智慧手机SoC市场释出最新的4月出货数据,整体的智能手机SoC出货量大约落在1,760万套,相较3月减少21.6%,也较去同期下降12.1%。法人认为,大陆本土智慧手机SoC在4月需求下滑的主要原因在于大陆开始在上海及

- 关键字:

联发科 高通 SoC

- 新思科技(Synopsys, Inc.)近日正式推出全新DesignDash设计优化解决方案,以扩展其EDA数据分析产品组合,通过机器学习技术来利用此前未发掘的设计分析结果,从而提高芯片设计的生产力。作为新思科技业界领先的数字设计系列产品和屡获殊荣的人工智能自主设计解决方案DSO.ai™的重要补充,新思科技DesignDash解决方案能够实现全面的数据可视化和AI自动优化设计,助力提高先进节点的芯片设计生产力。该解决方案将为所有开发者提供实时、统一、360度视图,以加快决策过程,通过更深入地了解运行、设计

- 关键字:

SoC 设计 新思科技 DesignDash

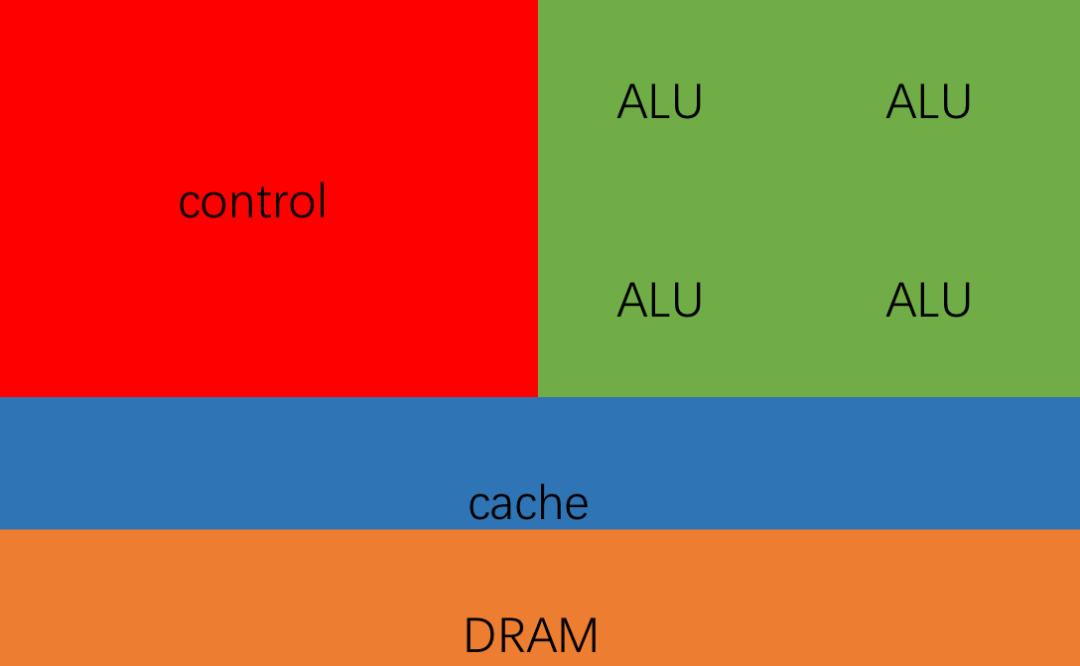

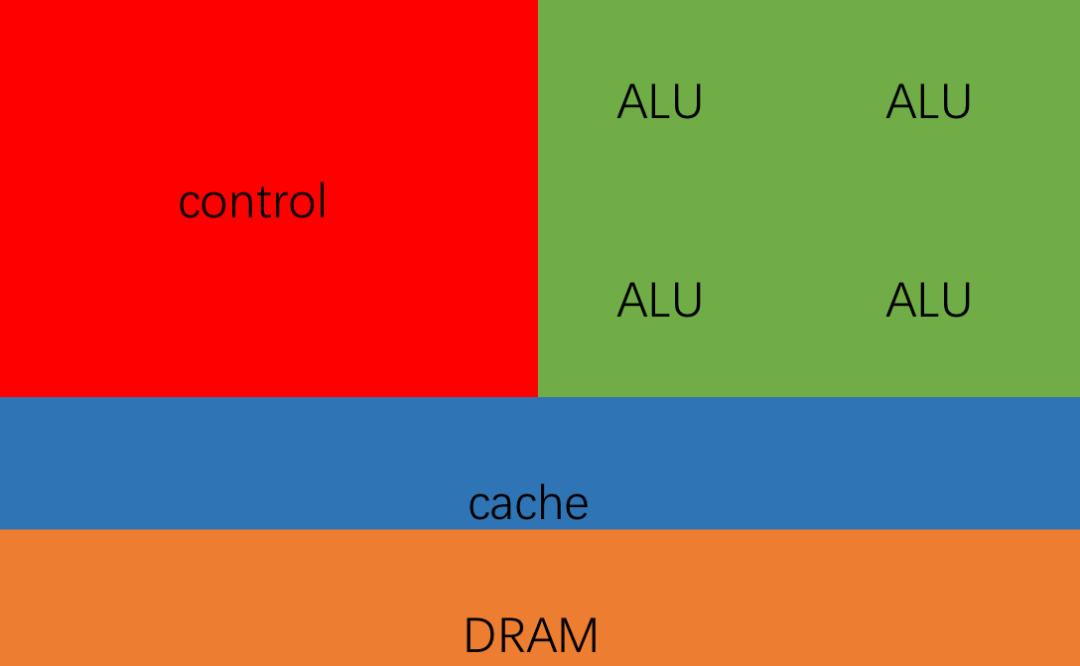

- 当汽车进入电动化、智能化赛道后,产品变革所衍生的名词困扰着消费者。例如关于芯片方面的CPU、GPU、NPU、SOC等等。这些参数格外重要,甚至不逊于燃油车时代的一些核心部件配置。 这次,我们进行一次芯片名词科普,一起扫盲做个电动化汽车达人。 关于芯片里的名词 1、CPU 汽车cpu是汽车中央处理器。其事就是机器的“大脑”,也是布局谋略、发号施令、控制行动的“总司令官”。 CPU的结构主要包括运算器(ALU,Arithmetic and Logic Unit)、控制单元(CU,Control

- 关键字:

NPU GPU SoC

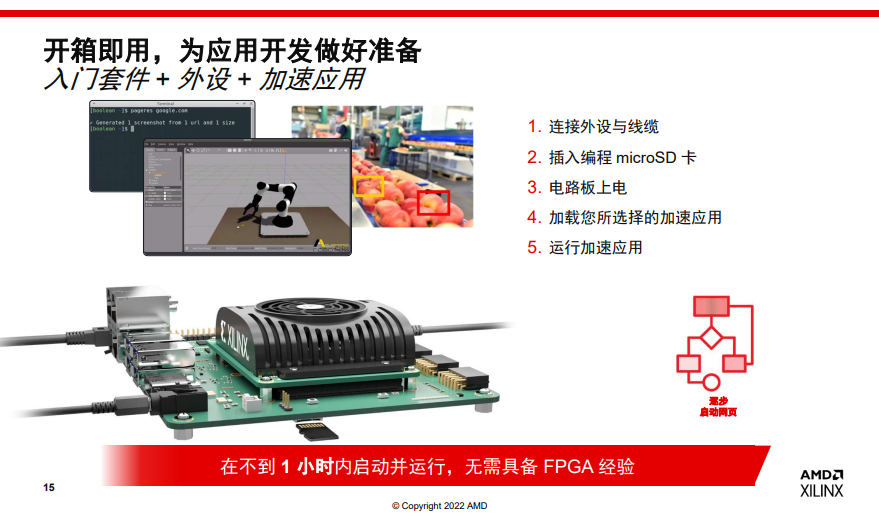

- 方案描述:本方案描述了Xilinx FPGA在汽车倒车显示上的应用。系统采用I2C实现对CMOS Sensor的控制,将采集的数据进行校正,阴影移除,缩放后通过TFT显示出来。使用Picoblaze实现对系统的灵活控制和算法运用,外挂SDRAM或Flash对图像进行存储。方案设计图:方案关键器件表:

- 关键字:

Xilinx FPGA 汽车电子

- 当前,全球汽车产业正在经历着重大变革,伴随着ADAS/自动驾驶、V2X等领域创新应用的不断增加,智能网联汽车正在成为具备中央处理引擎的重型计算机。 这背后,智能网联汽车的连接性、复杂性日益增加,随之而来的还有庞大的行驶数据和敏感数据,潜在的安全漏洞点也日趋增多。 公开数据显示,目前一辆智能网联汽车行驶一天所产生的数据高达10TB,这些数据不仅包含驾乘人员的面部表情等数据,还包含有车辆地理位置、车内及车外环境数据等。 多位业内人士直言,网关、控制单元、ADAS/自动驾驶系统、各类传感器、车载信息娱

- 关键字:

ASIL SoC ADAS

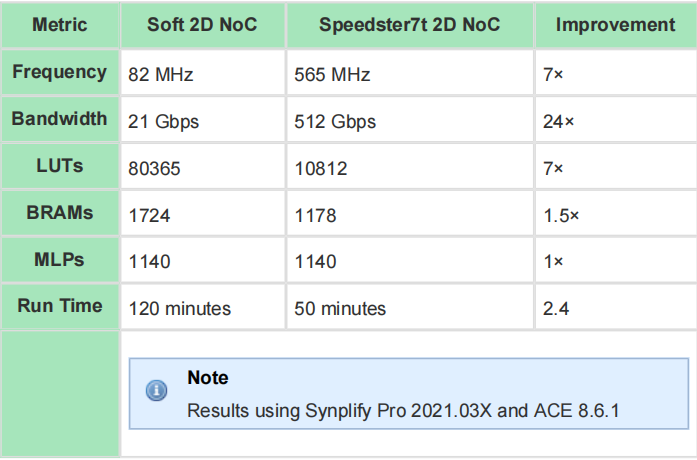

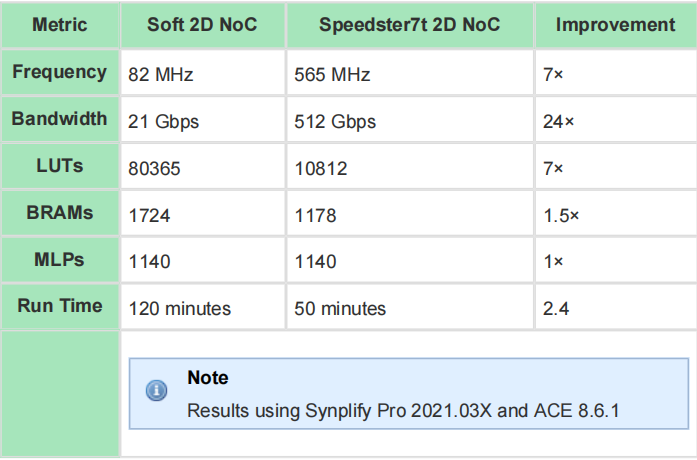

- 摘要随着旨在解决现代算法加速工作负载的设备越来越多,就必须能够在高速接口之间和整个器件中有效地移动高带宽数据流。Achronix的Speedster®7t独立FPGA芯片可以通过集成全新的、高度创新的二维片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了这两种实现2D NoC的方法,并提供了一个示例设计,以展示与软2D NoC实现相比,Achronix 2D

- 关键字:

Achronix FPGA 2D NoC

- 不到五年时间,AI芯片经历了概念炒作、泡沫破灭、修正预期和改进问题。有人担忧AI芯片的未来,也有人坚定看好。多位AI芯片公司的CEO都告诉笔者,AI芯片一直在持续发展,落地的速度确实比他们预期的慢。

- 关键字:

AI芯片 SoC 市场分析

- 四大类人工智能芯片(GPU、ASIC、FGPA、类脑芯片)及系统级智能芯片在国内的发展进度层次不齐。用于云端的训练、推断等大算力通用 芯片发展较为落后;适用于更多垂直行业的终端应用芯片如自动驾驶、智能安防、机器人等专用芯片发展较快。超过80%中国人工智能产业链企 业也集中在应用层。 总体来看,人工智能芯片的发展仍需基础科学积累和沉淀,因此,产学研融合不失为一种有效的途径。研究主体界定:面向人工智能领域的芯片及其技术、算法与应用无芯片不AI , 以AI芯片为载体实现的算力是人工智能发展水平的重要衡

- 关键字:

AI芯片 GPU ASIC FPGA 行业研究

- 高性能现场可编程逻辑门阵列(FPGA)和嵌入式FPGA(eFPGA)半导体知识产权(IP)领域的领导性企业Achronix半导体公司宣布:公司已任命江柏汉先生为全球销售副总裁。江先生为Achronix带来了超过30年的半导体产品销售经验,并将领导Achronix全球销售组织体系。在加入Achronix之前,江先生曾在Marvell半导体公司担任销售副总裁兼中国区总经理并常驻上海。在Marvell,江先生通过赢得一些战略性的项目和提高市场份额,成功地加快了公司业务的增长,同时对多项收购和资产剥离进行了整合和

- 关键字:

Achronix FPGA

- 莱迪思半导体宣布其CrossLink-NX FPGA和专为AI优化的软件解决方案,将用于联想最新的ThinkPad X1系列笔记本电脑中。全新的联想ThinkPad产品系列采用莱迪思充分整合的客户端硬件和软件解决方案,能够在不损失效能或电池使用时间的情况下提供优化的使用者体验,包括沉浸式互动、更好的隐私保护和更高效的协作。 莱迪思FPGA助力联想新一代网络边缘AI体验莱迪思营销和业务发展副总裁Matt Dobrodziej表示:「我们的AI优化解决方案产品旨在满足希望实现更高智能的各种网络边缘应

- 关键字:

莱迪思 FPGA 联想 边缘AI

- 针对固体火箭发动机推进剂药柱应变量大、高频振动时应变不易测量的问题,基于FPGA和柔性应变计设计了柔性应变测量装置。柔性应变计的测量范围大,可以测量双向应变,解决了推进剂药柱应变测量的难题。FPGA具有实时性高、并行运行的优点,解决了多路应变实时采集的难题。该应变测量装置还可用于其他高分子材料的应变测量。

- 关键字:

推进剂 柔性应变计 FPGA 高频振动 高速采集 202111

- 昨晚,博主 数码闲聊站爆料,明年是联发科冲击高端市场的关键一年,联发科下一代旗舰芯片将是前期唯一一款基于台积电4nm工艺打造的产品。 此前披露的信息显示,联发科下一代旗舰Soc可能会命名为天玑2000。 据爆料,天玑2000将采用超大核+大核+小核的三丛核架构,其中超大核为Cortex X2,与目前的Cortex-X1相比,Cortex-X2在指令集升级为ARMv9-A的同时,还针对分支预测与预取单元、流水线长度、乱序执行窗口、FP/ASIMD流水线、载入存储窗口和结构等进行了专门优化,提升处理效

- 关键字:

联发科 Soc

- 近日,物联网智能终端系统SoC芯片提供商芯翼信息科技(上海)有限公司(以下简称:芯翼信息科技或公司)完成近5亿元B轮融资,资金主要用于加强芯片产品研发、完善生产制造供应链、扩充核心团队等。本轮投资由招银国际、中金甲子联合领投,招商局资本、宁水集团、亚昌投资等跟投,另外老股东峰瑞资本、晨道资本、华睿资本等持续加注。芯翼信息科技成立于2017年,是一家专注于物联网智能终端系统SoC芯片研发的高新技术企业,产品涵盖通讯、主控计算、传感器、电源管理、安全等专业领域。公司创始人及核心研发团队来自于美国博通、迈凌、瑞

- 关键字:

芯翼信息 智能终端 SoC

fpga soc介绍

您好,目前还没有人创建词条fpga soc!

欢迎您创建该词条,阐述对fpga soc的理解,并与今后在此搜索fpga soc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473