- 目前在市场上我们可以采购到很多霍尔-ASIC传感器,我们可以用这些传感器来测量位置、磁场以及电流。所有这些ASIC传感器大多用于进行精确快速的电流测量,比如电力电子行业,对于电磁干扰具有高抗干扰性的优点。 这一

- 关键字:

电流 传感器 新一代 技术 ASIC 采用

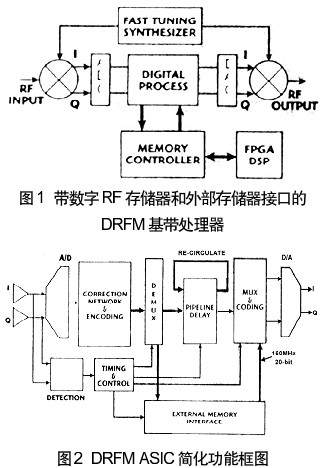

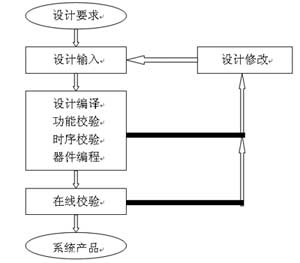

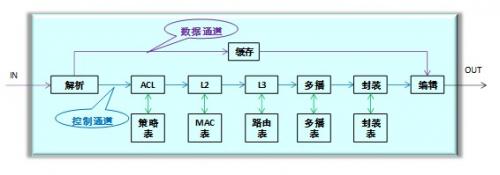

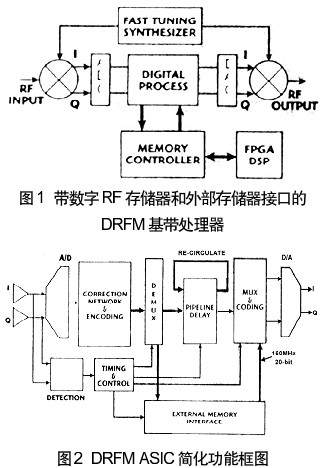

- 数字RF存储器(DRFM)用于现代脉冲压缩雷达中合成相干信号的再生。DRFM系统有很多不同的实现方法。图1示出1个特殊的类型,它是1个双边带,4位,相位取样系统,它的瞬时带宽为500MHz。采用0.18祄 CMOS 工艺制造的混合信号专用集成电器(ASIC)可实现系统的基带元件,这包括相位取样电路、数字处理、信号重建和数/模输出。

- 关键字:

RF ASIC

- 尽管现在还面临国际金融危机的考验,但业界仍然看好今年的视频监控市场。网络视频监控技术的应用,又将产业发展带到了一个新的高度,它将引领产业的又一次变革。用户对图像清晰度、处理速度和智能分析方面更高的要求,将促使视频监控技术向高清化、系统化、智能化发展,这已经成为当前技术发展的重要方向。

中国视频监控市场规模预测(2007-2012)

数据来源:IDC

- 关键字:

金融危机 视频 监控 IP DSP ASIC

- 现代汽车中的电子设备不断增多,因而越来越需要采用良好的设计,以满足主要的电磁兼容性标准的要求。同时,越来越...

- 关键字:

ASIC ASSP 电磁兼容 芯片

- 基于MCU、定制ASIC和体积庞大的电线束来实现引擎及控制电子的系统方案已发展至接近其技术和应用极限,汽车工 ...

- 关键字:

MCU 引擎控制单元 ASIC

- 近几年,数字音频市场发展非常迅速。独立式音频与多媒体播放器近几年已成为数字音频市场的主流。数以百万计的消费者都在想办法将其便携式播放器与家用音响和车载立体声音响进行最佳连接。这激励着目前的家用和车载音频设备厂商为迎接数字时代的到来而开始准备他们的HiFi系统。为了满足人们对播放器不断提高的要求,市场上也出现了大量芯片或芯片组。但这些进入数字音频市场的芯片往往有很多缺陷,问题就出在合适处理硬件的选择方面。

传统解决方案

有些厂商试图将计算机的一些组件用于音频或多媒体播放器。尽管这些组件在一台

- 关键字:

数字音频 ASIC NAND

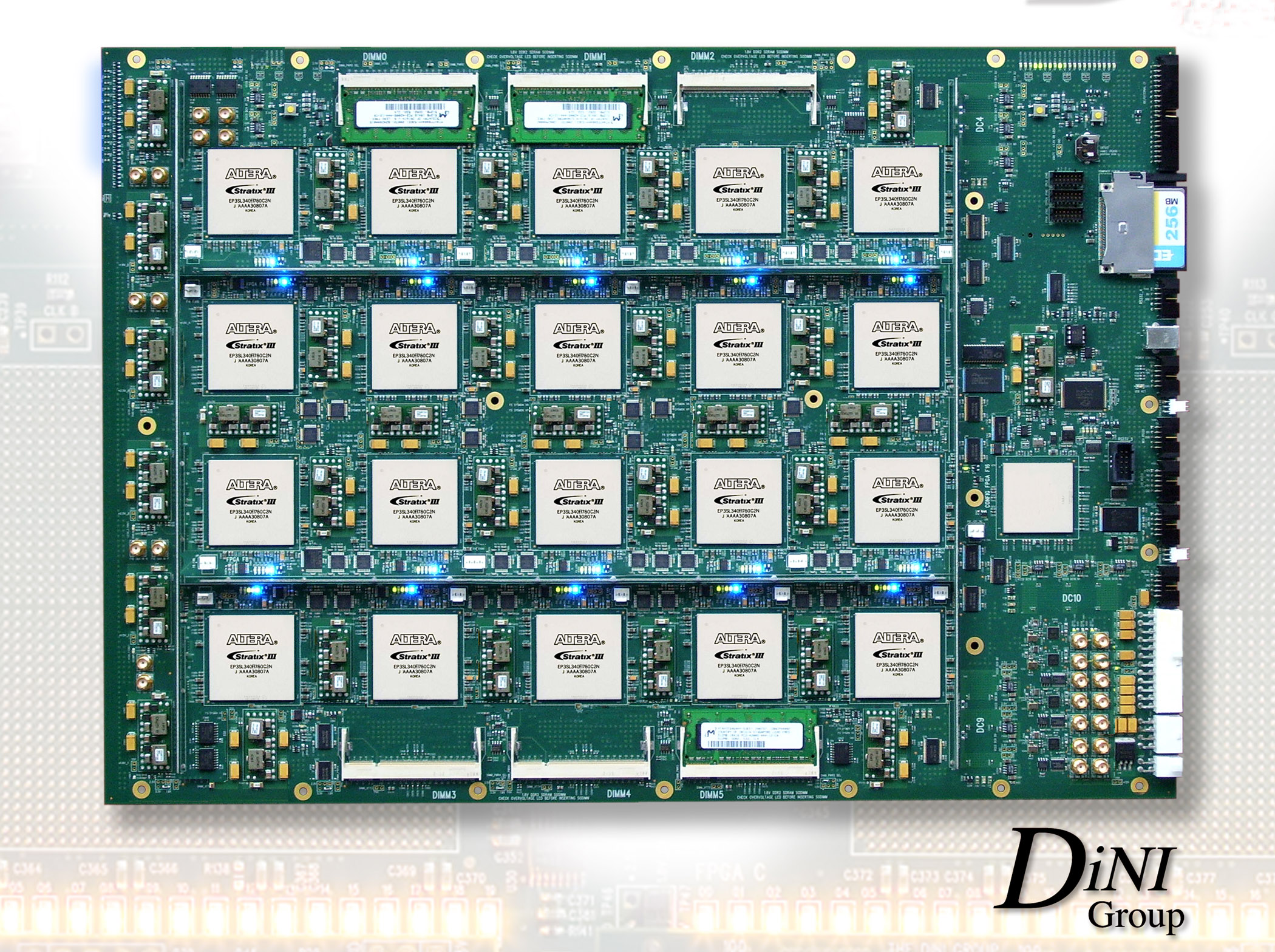

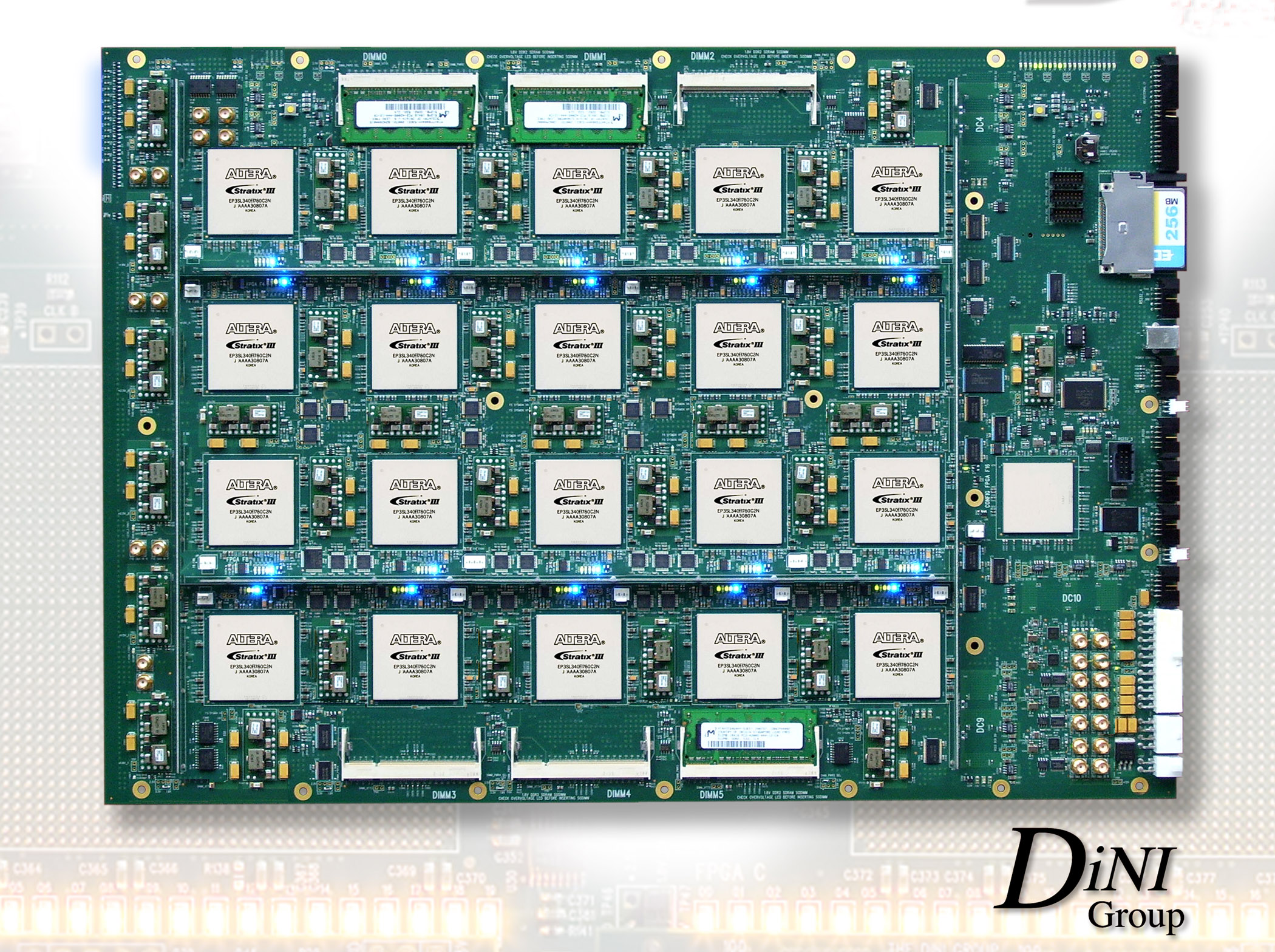

- 2008年11月11号,北京——Altera公司(NASDAQ: ALTR)今天宣布,Dini集团在其业界容量最大的单板FPGA原型引擎中采用了具有340K逻辑单元(LE)的Stratix® III EP3SL340 FPGA。DN7020K10采用了1,760引脚封装的20片EP3SL340 FPGA,每个器件提供1,104个用户I/O,容量等价于5千万ASIC逻辑门。客户设计无线通信、网络和图形处理应用等定制ASIC时,可以利用这一超大容量原型电路板来验

- 关键字:

Altera Dini集团 Altera Stratix III FPGA ASIC

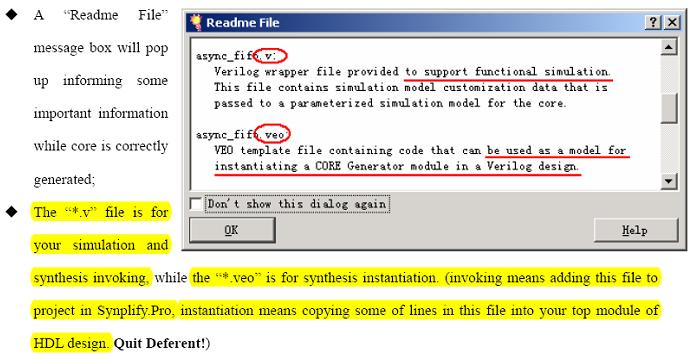

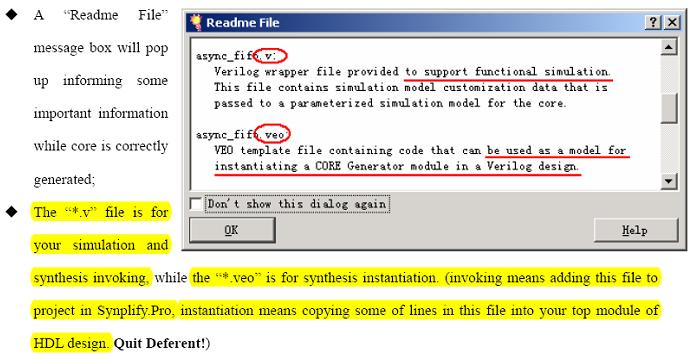

- IP核生成文件:(Xilinx/Altera 同)

IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit->Language Template->COREGEN 中找到verilog/VHDL 的例化方式)。asyn_fifo.v 是该核的行为模型,主要调用了 xilinx 行为模型库的模块,仿真时该文件也要加入工程。(在 ISE中点中该核,在对应的 processes 窗口中

- 关键字:

IP核

- 日前,Achronix 半导体公司宣布全球速度最快的 FPGA 现已开始供货。Speedster 系列的首款产品为 SPD60,该产品系列的速度可达 1.5 GHz,性能比现有 FPGA 提高了 3 倍。

参加 Achronix 早期试用合作的客户已经利用 Speedster 在需要类似 ASIC 性能的应用中取得了重大成功,这些应用包括网络、电信、测试与测量、加密以及其他高性能应用。Speedster 系列 FPGA 非常适用于上述各应用类型。

Achronix 与领先的合成技术厂商合作

- 关键字:

FPGA Achronix 半导体 ASIC

- 芯片是一个产业链的终结,也是另一个产业链的开始,而产业链起点的高度往往决定了产业整体发展的高度。

近日,在安捷伦公司的数字测量论坛上,虽然大会的主题是数字设计测量的未来发展,但安捷伦着力和大家分享的却是自己在示波器产品设计方面的理念和经验。安捷伦强调,要开发出高性能示波器必须具有自己开发专用芯片的能力,安捷伦可以在将示波器作为重点的这几年取得高速增长,根本在于原有的RF设计能力大幅提升了示波器产品的性能,使之快速赶上竞争对手的产品,即示波器产品的突破来源于芯片技术的提升。

一个以测试仪器为

- 关键字:

芯片 ASIC 数字测量 安捷伦 200809

- 引言

在传统的控制系统中,通常将单片机作为控制核心并辅以相应的元器件构成一个整体。但这种方法硬件连线复杂、可靠性差,且在实际应用中往往需要外加扩展芯片,这无疑会增大控制系统的体积,还会增加引入干扰的可能性。对一些体积小的控制系统,要求以尽可能小的器件体积实现尽可能复杂的控制功能,直接应用单片机及其扩展芯片就难以达到所期望的效果。

复杂可编程逻辑器件(CPLD)具有集成度高、运算速度快、开发周期短等特点,它的出现,改变了数字电路的设计方法、增强了设计的灵活性。基于此,本文提出了一种采用Alt

- 关键字:

CPLD 开发环境 单片机 元器件 VHDL ASIC

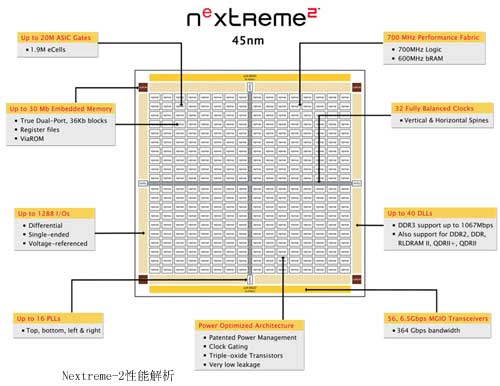

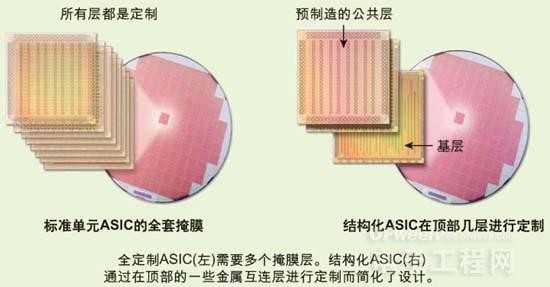

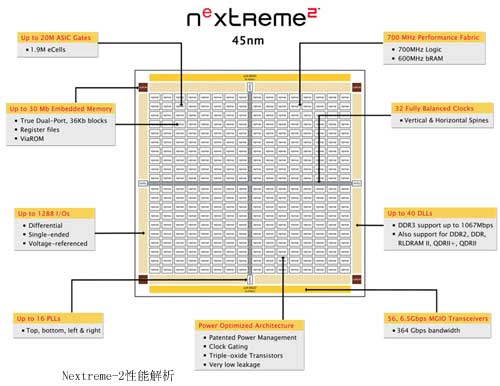

- 半导体调研机构Gartner多年来一直在跟踪ASIC设计项目数量,其趋势已经无疑被认定向下。最新技术的ASIC设计费用已经上升到一个很高点,以致许多中小规模的公司用不起而只能采用FPGA。而ASIC只有依靠正在研发的各种降低其设计费用的新方法才有希望挽回颓势。

拥有独特的过孔层布线定制专利技术以及零掩模费和无最低订货量限制的新结构化ASIC平台供应商eASIC在其90nm Nextreme ASIC产品的基础上,又发布了其新一代Nextreme-2系列产品。Nextreme-2系列是目前市面上唯

- 关键字:

ASIC FPGA 信号处理 富士通

- 世芯电子(Alchip Technologies)日前宣布与SONY半导体事业部(SONY Semiconductor Group)成为封装技术的合作伙伴,以提升其全球客户在先进SoC/ASIC解决方案方面的服务。

世芯总裁暨执行长关建英表示,今天的产品需要最小芯片尺寸、增加内存容量以及整合不同种类的内存在多芯片封装(Multi-Chip Package)上。透过SONY的先进技术以及世芯缩短产品上市时程的能力,我们将能协助客户使用更先进的解决方案。

世芯电子主要业务包含供多元化晶圆厂选择

- 关键字:

封装 世芯 SONY SoC ASIC

- 摘要:基于SOC应用,采用TSMC 0.18μm CMOS工艺,设计实现了一个低电压、高增益的恒跨导轨到轨运算放大器IP核。该运放采用了一倍电流镜跨导恒定方式和新型的共栅频率补偿技术,比传统结构更加简单高效。用Hspice对整个电路进行仿真,在1.8V电源电压、10pF负载电容条件下,其直流开环增益达到103.5dB,相位裕度为60.5度,输入级跨导最大偏差低于3%。

关键词:运算放大器;轨到轨;共栅频率补偿;IP核

1引言

在SOC的模拟集成电路设计中,使用简单的电路结构

- 关键字:

SOC 运算放大器 轨到轨 共栅频率补偿 IP核

asic ip核介绍

您好,目前还没有人创建词条asic ip核!

欢迎您创建该词条,阐述对asic ip核的理解,并与今后在此搜索asic ip核的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473