引 言

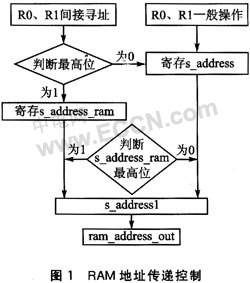

80C51系列单片机是一类经典的8位微处理器,其设计方法和体系结构一直是其他各类单片机设计的参考典范,自从20世纪80年代面世以后,得到了极大的发展与应用。直到今天,市场上还有一大部分单片机应用成品将其作为处理核心。基于80C51系列单片机无知识产权保护、市场应用广泛等优点,对其进行功能拓展,既有利于经济上节约成本,也有利于成果的推广使用。而随着单片机应用日趋复杂化,传统的51系列单片机在设计上的不足逐渐显现出来。如在现有128字节内部RAM基础上,处理一些比较复杂的算法就显不足。鉴于此

关键字:

RAM 单片机 微处理器 IP核 仿真测试

Catalyst半导体继续快速扩展电压监控产品线,为微处理器、微控制器,ASIC器件和其它系统处理器的应用新增一款高精度超低功耗5通道监控器件。5通道电压监控被整合于一个小尺寸的8引脚MSOP封装之内,CAT885能有效降低系统成本、节约电路板空间。

CAT885具备低有效漏极开路输出及手动复位输入的特点,可针对各种电子产品完成系统复位和监控功能。CAT885可以监控多达5通道的系统电压,若所有被监控的电源电压已经超过额定电平值,并且随后被启动的器件内部计时器超时溢出后,有效的复位输出才会终止,

关键字:

Catalyst 电压监控器 微处理器 微控制器 ASIC

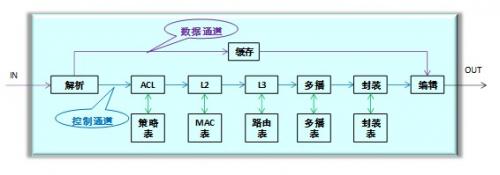

许多通信系统都要用到多速滤波器(multirate filter),多速滤波器是指输出数据速率与输入数据速率不相等的滤波器,常用于某个物理接口如数模转换器(DAC)或模数转换器(ADC)的接口处。

关键字:

ASIC DSP PLD 滤波器设计

世界级ASIC设计晶圆厂及定制解决方案供应商VeriSilicon Holdings Co., Ltd.(VeriSilicon)“已经加盟功耗前锋倡议”( Power Forward Initiative,PFI),计划为其ASIC客户提供基于通用功率格式(Common Power Format,CPF)的设计解决方案。

VeriSilicon采用Cadence低功耗解决方案,是业界领先的完整的设计流程,以Si2标准的CPF为基础,贯穿逻辑设计、验证、实现等技术。这种针

关键字:

晶圆 VeriSilicon ASIC 低功耗 CPF

IP(Intellectual Property),即常说的知识产权。在PLD领域中,IP核是指将数字系统中常用但比较复杂的一些功能块设计成参数可调并以HDL源文件或加密网表形式存在的可供其他用户直接调用的软件模块。由于已经过严格的测试和优化,使用IP核可以显著减小设计和调试时间,提高开发效率,降低产品成本。本文以一款结构经参数化的全功能硬件扫描键盘控制器的开发为例,阐述IP核设计的一般方法与步骤。

1 设计的意义与可行性

键盘是计算机系统中最常用的人机交互输入设备。在嵌入式系统中,用R+

关键字:

扫描键盘,IP核

ASIC和SoC器件成本的逐步上升迫使半导体供应商必须进一步开拓各个器件的市场以寻求满意的投资回报。日益增长的软件使用为此提供了有效的机制,因为增加的软件内容等同于更多的功能和软件变化提供了特定市场产品的差异化。

关键字:

ASIC SoC 原型设计 软件技术

本文设计了一种基于FPGA的UART核,该核符合串行通信协议,具有模块化、兼容性和可配置性,适合于SoC应用。

关键字:

FPGA UART IP核

随着人们对安全需求的日益重视和性能的不断增强、价格的迅速降低,应用市场正快速膨胀。但是不管是定位于中小企业、中小网络的DVR解决方案,还是定位在高端、企业级用户的DVS,以及广被业界看好的IP摄像机,都对方案提供商提出了更高的要求(更多挑战):更高的视频信号分辨率和压缩比;更灵活的媒体格式支持;更安全的内容保护;更低的功耗、成本和开发复杂度。

在视频监控应用领域主要包括媒体处理器、DSC、ASIC、以及FPGA等几种方案。其中DSC虽然具有部分DSP的功能,但是从总体来讲,DSC和媒体处理器一样

关键字:

视频监控 DVS DSC ASIC

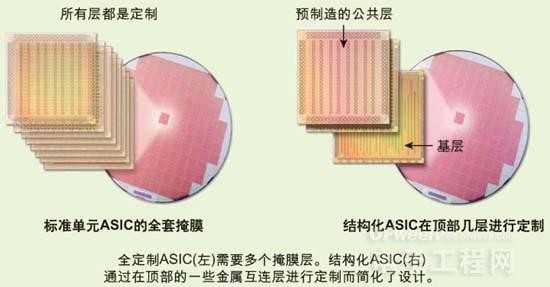

目前ASIC的现状并不让人看好,但是相信通过创新,设计出真正的差异化产品,ASIC仍有希望。

曾经喧嚣的ASIC(专用集成电路),在初创IC(集成电路)设计公司数量减少以及设计成本居高不下的情况下正经历轻度的衰退。

那些 ASIC制造商,如LSILogic、Fujitsu(富士通)、NEC、Oki、

关键字:

ASIC ASSP

暴露在恶劣的太空环境下的系统必须能在各种极端的条件下正常工作,且不丧失任何功能。太空系统在其生命期内采集的信息若有任何微小偏差,都可能会对整个数据作出错误的诠释。由于这些太空系统都是执行特别重要任务的系统,在设计时就必须考虑多个因素,除了功耗、系统重量、体积和发射时间等因素外,系统的可靠性是最主要关键。例如,执行太空任务的卫星必须能够在整个生命期内 (通常是数十年) 耐受各种恶劣的环境条件。就可靠性而言,在太空运行的系统面临最大的挑战也许是持续的辐射轰击。提高系统的耐辐射能力正迅速成为系统工程师的一项

关键字:

Actel FPGA 耐辐射 RH-ASIC

引言

随着VLSI设计技术和深亚微米制造技术的飞速发展, SOC (System on Chip ) 技术逐渐成为了集成电路设计的主流技术。SOC 已经在便携式手持设备、无线网络终端和多媒体娱乐设备等领域得到了广泛的应用。

高性能的处理器核是SOC设计中最为关键和核心的部分。绝大多数SOC 的处理器都采用了RISC体系结构。RISC 处理器具有指令效率高、电路面积小和功率消耗低等特点, 满足了SOC 高性能、低成本和低功耗的设计要求。目前在SOC 设计中广泛使用的32bit RISC 处理

关键字:

内核 RISC 处理器 IP核

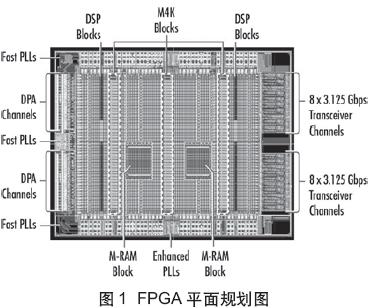

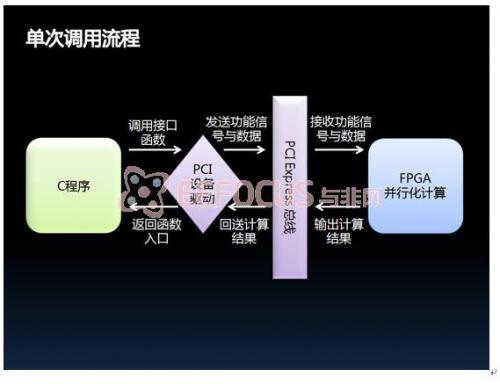

Altera公司对PCI Express,串行Rapid I/O和SerialLite等串行标准和协议的认可,将促进具有时钟和数据恢复(CDR)功能的高速串行收发器的应用。这些曾在4或8位ASSP中使用的收发器现在可以集成在高端FPGA中。带有嵌入式收发器的FPGA占据更小的电路板空间,具有更高的灵活性和无需接口处理的两芯片方案等优势,因此,采用这种FPGA对电路板设计者是很具有吸引力的选择。

在FPGA中集成收发器使得接口电路处理工作由电路板设计者转向芯片设计者。本文阐述在一个FPGA中集成1

关键字:

Altera FPGA ASSP ASIC

与通用集成电路相比,ASIC芯片具有体积小、重量轻、功耗低、可靠性高等几个方面的优势,而且在大批量应用时,可降低成本。现场可编程门阵列(FPGA)是在专用ASIC的基础上发展出来的,它克服了专用ASIC不够灵活的缺点。与其他中小规模集成电路相比,其优点主要在于它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便。DSP+FPGA结构最大的特点是结构灵活,有较强的通用性,适于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展,适合于实时数字信号处理。本

关键字:

ASIC

可编程逻辑器件(PLD)在与ASIC之激战中已经告捷:每年开始PLD设计的项目数目远远高于ASIC项目开工数。同时,PLD厂家之间也发生微妙的变化,由崛起时的争强好斗和互不相让,渐渐找到了各自的落脚点。目前看来,Xilinx的产品稳居65nm FPGA市场,Altera最大的量产在90nm FPGA,Actel凭低功耗0.13微米FPGA在对功耗要求苛刻的领域站稳了脚跟。昔日的两个庞然大物——Xilinx和Altera之间拉开了距离,同时小型FPGA厂商如Actel跃跃欲试,渐渐跳

关键字:

PLD FPGA ASIC

前言

高性能、高容量FPGA在ASIC/SoC原型设计及系统两方面的应用持续增长。这些设计通常包括硬件及嵌入式软件(也可能包括应用软件)的复杂组合,这给系统验证带来了巨大负担,原因是检测、隔离、调试及校正故障要比最初设计所花费的时间、资金和工程资源多得多。

由于软硬件之间交互作用相当复杂且无法预见,仅仅是找到深藏于系统中的故障就需要进行长时间的测试序列,而且随后的调试过程还需要花费更多的时间及精力。另外,如果验证测试使用视频流等实际数据时,那么间发故障将很难(如果并非不可能)重现。

关键字:

FPGA ASIC 模拟器

asic ip核介绍

您好,目前还没有人创建词条asic ip核!

欢迎您创建该词条,阐述对asic ip核的理解,并与今后在此搜索asic ip核的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473