- 一. 引言

随着人类对于居住环境要求的不断提高,目前PCB生产过程中涉及到的环境问题显得尤为突出。目前有关铅和溴的话题是最热门的;无铅化和无卤化将在很多方面影响着PCB的发展。虽然目前来看,PCB的表面处理工

- 关键字:

PCB 表面处理 工艺

- 本文以比较器为基本电路,采用恒流源充放电技术,设计了一种基于1.0mu;m CMOS工艺的锯齿波振荡电路,并对其各单元组成电路的设计进行了阐述。同时利用Cadence Hspice仿真工具对电路进行了仿真模拟,结果表明,锯

- 关键字:

CMOS 工艺 锯齿波 振荡电路

- 1 引言 本文在传统锁相环结构的基础上进行改进,设计了一款用于多路输出时钟缓冲器中的锁相环,其主 要结构包括分频器、鉴频鉴相器(PFD)、电荷泵、环路滤波器和压控振荡器(VCO)。在鉴相器前采用预 分频结构减小

- 关键字:

CSMC PLL 工艺 零延时

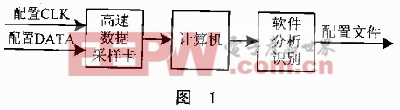

- 在现代电子系统设计中,由于可编程逻辑器件的卓越性能、灵活方便的可升级特性,而得到了广泛的应用。由于大规模高密度可编程逻辑器件多采用SRAM工艺,要求每次上电,对FPGA器件进行重配置,这就使得可以通过监视配置

- 关键字:

保密性 问题 FPGA 工艺 SRAM 基于

- 利用PLC系统控制闪光对焊工艺过程的设计,闪光对焊作为一种先进的焊接技术,具有无需添加焊接材料、生产率高、成本低、易于操作等优点。随着工业技术的不断发展,焊接的零件截面越来越大,遇到了一些技术问题,如焊接加热难、生产率低、产品合格率低等。为了

- 关键字:

工艺 过程 设计 闪光 控制 PLC 系统 利用

- 工业以太网是一个基于以太网技术标准进行实现所有控制、调节仪器设备自动化技术的高层次概念。因为一般情况下企业已拥有把办公计算机连接成为一个网络的LAN以太网了,而这种网络有可能与工业以太网联网,并且仍然使用

- 关键字:

设计 方案 联网 垂直 工艺 设备 流程

- 实现世界上最先进的定制逻辑器件引言

Altera于2008年第二季度推出Stratix® IV和HardCopy® IV器件系列标志着世界上首款40-nm FPGA和业界唯一

40-nm ASIC 无风险移植途径的诞生。Altera 通过三年周密的规划和

- 关键字:

40 nm 工艺 定制

- SMT小型电子产品的安装是高等职业学校应用电子技术专业中《电子产品工艺实训》课程的一个重要项目。结合《电子产品工艺》这门课程的特点,我们在电子实训环节采用了项目教学模式,即师生双方共同在实训室参与项目教学

- 关键字:

环节 应用 工艺 电子 教学 项目

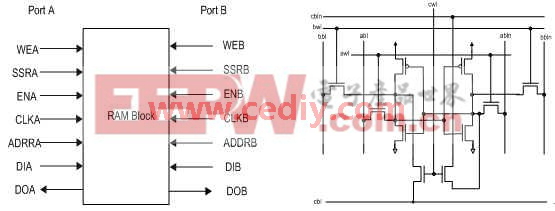

- 基于0.13微米CMOS工艺下平台式FPGA中可重构RAM模块的一种设计方法,1. 引言

对于需要大的片上存储器的各种不同的应用,FPGA 需要提供可重构且可串联的存储器阵列。通过不同的配置选择,嵌入式存储器阵列可以被合并从而达到位宽或字深的扩展并且可以作为单端口,双端口

- 关键字:

RAM 重构 模块 设计 方法 FPGA 平台 0.13 微米 CMOS 工艺

- 0 引言

运算放大器是数据采样电路中的关键部分,如流水线模数转换器等。在此类设计中,速度和精度是两个重要因素,而这两方面的因素都是由运放的各种性能来决定的。

本文设计的带共模反馈的两级高增益运

- 关键字:

CMOS 工艺 放大器 全差分

- 针对DC-DC电源管理系统中所必须的欠压锁存(UVLO)功能,提出一种改进的欠压锁存电路。所设计的电路在不使用额外的带隙基准电压源作为比较基准的情况下,实现了阈值点电位、比较器的滞回区间等参量的稳定。整个电路采用CSMC0.5 μm BCD工艺设计,使用HSpice软件仿真,结果表明所设计的UVLO电路具有结构简单、反应灵敏、温度漂移小、功耗低等特点。

- 关键字:

电路设计 工艺 BCD 基于

- 半导体设备和材料企业的技术提升及创新要从研究材料入手,从源头上达到国际先进水平。在工业制备方面要加强新型工艺的开发和应用。我国半导体设备性能、控制已达到国际高端水平,但稳定性还待提升。另外,需要做高端设备工艺方面的提升和研究。

兰州瑞德自主开发的产品涉及多行业、多领域,在国际金融危机期间,遇到的问题主要在工艺应用和需求行业比例发生变化方面,公司根据各行业特点,公司采取新品上市、设备改制、设备派生等手段,使研、切、抛电子专用设备进入各行业的速度加快了,尤其是视窗、光学等行业。半导体行业仍主打高端设

- 关键字:

半导体设备 工艺

- 近年来,软件无线电(Software Radio)的技术受到广泛的关注。理想的软件无线电台要求对天线接收的模拟信号经过放大后直接采样,但是由于通常射频频率(GHz频段)过高,技术上所限难以实现,而多采用中频采样的方法。而对

- 关键字:

Telescopic 0.13 CMOS 工艺

- 基于美国联邦通讯委员会(FCC)的E911定向和定位业务(LBS),期望紧跟这一标准的全球定位系统(GPS)接收机随时准备在无线通信中扮演一个至关重要的角色。成功的E911/LBS产品与业务将会需要具有以下特征的解决方案:能在移

- 关键字:

SiGe GPS 工艺 接收机

- 三星电子公司执行副总裁兼研发中心总经理Kinam Kim在近日IMEC技术论坛上表示,业界有人认为芯片特征尺寸微缩极限在5nm左右,而他并不同意这一说法,他相信存在众多可能的途径来克服硅微缩过程中所遇到的障碍,使硅产业越过纳米量级。

- 关键字:

三星 硅 5nm

5nm 工艺介绍

您好,目前还没有人创建词条5nm 工艺!

欢迎您创建该词条,阐述对5nm 工艺的理解,并与今后在此搜索5nm 工艺的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473