- 基于0.13微米CMOS工艺下平台式FPGA中可重构RAM模块的一种设计方法,1. 引言

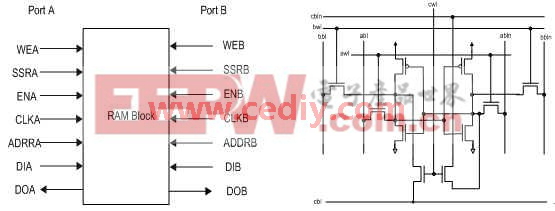

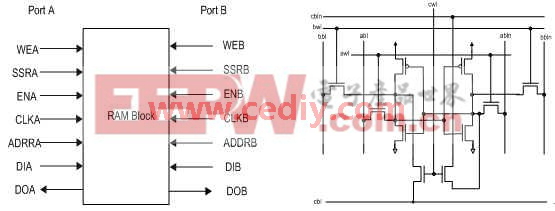

对于需要大的片上存储器的各种不同的应用,FPGA 需要提供可重构且可串联的存储器阵列。通过不同的配置选择,嵌入式存储器阵列可以被合并从而达到位宽或字深的扩展并且可以作为单端口,双端口

- 关键字:

RAM 重构 模块 设计 方法 FPGA 平台 0.13 微米 CMOS 工艺

- 0 引言

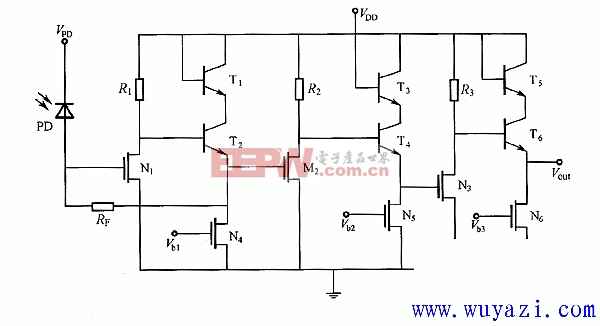

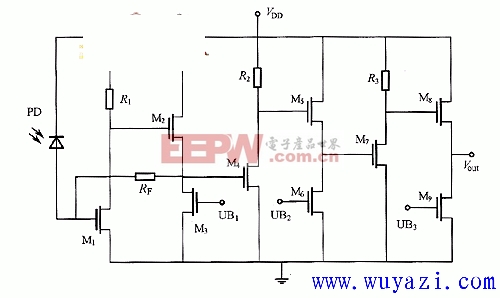

运算放大器是数据采样电路中的关键部分,如流水线模数转换器等。在此类设计中,速度和精度是两个重要因素,而这两方面的因素都是由运放的各种性能来决定的。

本文设计的带共模反馈的两级高增益运

- 关键字:

CMOS 工艺 放大器 全差分

- 针对DC-DC电源管理系统中所必须的欠压锁存(UVLO)功能,提出一种改进的欠压锁存电路。所设计的电路在不使用额外的带隙基准电压源作为比较基准的情况下,实现了阈值点电位、比较器的滞回区间等参量的稳定。整个电路采用CSMC0.5 μm BCD工艺设计,使用HSpice软件仿真,结果表明所设计的UVLO电路具有结构简单、反应灵敏、温度漂移小、功耗低等特点。

- 关键字:

电路设计 工艺 BCD 基于

- 半导体设备和材料企业的技术提升及创新要从研究材料入手,从源头上达到国际先进水平。在工业制备方面要加强新型工艺的开发和应用。我国半导体设备性能、控制已达到国际高端水平,但稳定性还待提升。另外,需要做高端设备工艺方面的提升和研究。

兰州瑞德自主开发的产品涉及多行业、多领域,在国际金融危机期间,遇到的问题主要在工艺应用和需求行业比例发生变化方面,公司根据各行业特点,公司采取新品上市、设备改制、设备派生等手段,使研、切、抛电子专用设备进入各行业的速度加快了,尤其是视窗、光学等行业。半导体行业仍主打高端设

- 关键字:

半导体设备 工艺

- 近年来,软件无线电(Software Radio)的技术受到广泛的关注。理想的软件无线电台要求对天线接收的模拟信号经过放大后直接采样,但是由于通常射频频率(GHz频段)过高,技术上所限难以实现,而多采用中频采样的方法。而对

- 关键字:

Telescopic 0.13 CMOS 工艺

- 基于美国联邦通讯委员会(FCC)的E911定向和定位业务(LBS),期望紧跟这一标准的全球定位系统(GPS)接收机随时准备在无线通信中扮演一个至关重要的角色。成功的E911/LBS产品与业务将会需要具有以下特征的解决方案:能在移

- 关键字:

SiGe GPS 工艺 接收机

- 三星电子公司执行副总裁兼研发中心总经理Kinam Kim在近日IMEC技术论坛上表示,业界有人认为芯片特征尺寸微缩极限在5nm左右,而他并不同意这一说法,他相信存在众多可能的途径来克服硅微缩过程中所遇到的障碍,使硅产业越过纳米量级。

- 关键字:

三星 硅 5nm

- 从现有市场行情来看,国内多晶硅价格下跌的趋势将难以改变。国内可将生产成本压低到50美元/公斤以下的多晶硅企业,几乎是凤毛麟角。

森松集团(中国)(下称“森松”)董事总经理薛绛颖接受记者专访时表示,目前中国的多晶硅设备制造已较为成熟。而国内多晶硅生产商的管理、技术及工艺都有待提高,这样才能有效控制成本。

装备技术尤为关键。以森松集团为例,作为国内最大的多晶硅工艺成套设备供应商,约有80%的国内多晶硅厂,都使用其成套设备如还原炉以及相关技术。

该公司生产的还原炉要

- 关键字:

工艺 多晶硅

- 新华网北京3月27日电记者 27日从科技部获悉,我国“极大规模集成电路制造装备及成套工艺”重大专项进入全面实施阶段。

据介绍,“极大规模集成电路制造装备及成套工艺”重大专项旨在开发集成电路关键制造装备,掌握具有自主知识产权的成套先进工艺及相关新材料技术,打破我国高端集成电路制造装备与工艺完全依赖进口的状况,带动相关产业的技术提升和结构调整。

重大专项是实现我国中长期科技发展规划的一项重要内容,党中央、国务院高度重视重大专项的实施工作,多次召开

- 关键字:

集成电路 工艺

- 应答器设计的成本依赖于几个因素,而不仅仅是硅的成本。事实上,芯片制造工艺的成本(就其复杂性和成熟程度...

- 关键字:

功耗 低功耗 驱动 工艺 温度 电压

- 压控振荡器(VCO)是射频集成电路(RF-ICs)中的关键模块之一。近年来随着无线通信技术的快速发展,射频收发机也有了新的发展趋势,即单个收发机要实现宽频率多标准的覆盖,例如用于移动数字电视接收的调谐器一般要实现T-DMB、DMB-T等多个标准,并能覆盖VHF、UHF和LBAND等多个频段。本文所介绍的VCO设计采用如图1(a)所示的交叉耦合电感电容结构,相对于其他结构的VCO来说该结构更加易于片上集成和实现低功耗设计,并且利用LC谐振回路的带通滤波特性,能获得更好的相位噪声性能。

- 关键字:

宽带 LC VCO 设计 相噪 工艺 0.18 RF CMOS 基于

- 本文基于Peregrine(派更)半导体公司的单片数字步进衰减器(DSA,Digital Step Attenuator)产品系列,阐述了DSA通用设计方法、RF CMOS工艺以及这些器件的性能。

- 关键字:

CMOS 工艺 步进 数字

- IBM联盟开发出可在32纳米芯片中加速实现一种被称为“high-k/metal gate(高电介质金属栅极)”的突破性材料。这种新方法是基于被称为“high-k gate-first(高电介质先加工栅极)”加工工艺的方法,为客户转向高电介质金属栅极技术提供了一种更加简单和更省时间的途径,由此而能够带来的益处包括性能的提高和功耗的降低。通过使用高电介质金属栅极,IBM与联盟合作伙伴成功地开发出比上一代技术体积小50%的芯片,同时提高了众多性能。使用这种新技术的

- 关键字:

制程 工艺

- 资深评论人 莫大康

按国际工艺路线图指引,全球半导体07年才进入45纳米制程。其中英特尔首先采用高k及金属栅工艺,将CMOS工艺推向一个新的里程碑。连戈登摩尔也坦诚,由此将定律可延伸又一个10年。

此次中芯国际能成功与国际最先进的技术输出者,IBM达成45纳米的技术转让协议意义十分深远。

首先表征中芯国际愿意继续追赶国际最先进工艺水平,加入全球最先进

- 关键字:

45纳米 中芯国际 IBM 工艺

5nm 工艺介绍

您好,目前还没有人创建词条5nm 工艺!

欢迎您创建该词条,阐述对5nm 工艺的理解,并与今后在此搜索5nm 工艺的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473