- 模拟 EE 世界失去了一颗明星。Jim 的数百篇文章、书籍和应用笔记是(并将继续是)信息、灵感和看到大师轻松解决棘手设计难题的喜悦的无底泉源,所有这些都包含在令人愉快的写作风格中。这里介绍的设计思想源自他发表在 AN45测量和控制电路集(夜班尿布和设计)第 7 页的电路之一。模拟 EE 世界失去了一颗明星。Jim 的数百篇文章、书籍和应用笔记是(并将继续是)信息、灵感和看到大师轻松解决棘手设计难题的喜悦的无底泉源,所有这些都包含在令人愉快的写作风格中。这里介绍的设计思想源自他发表在 AN45测量和控制电路

- 关键字:

晶体管 VBE 振荡器

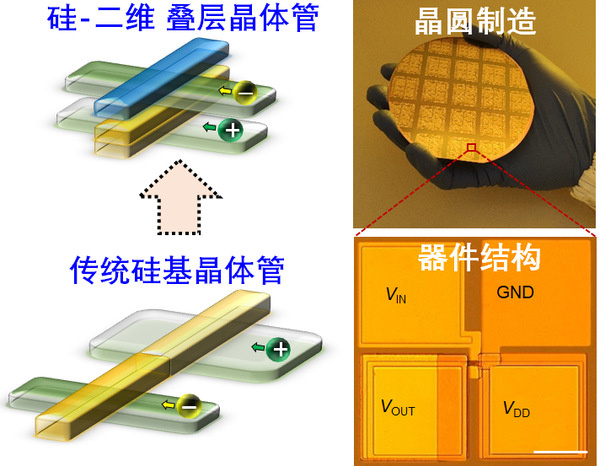

- IT之家 12 月 11 日消息,众所周知,传统集成电路技术使用平面展开的电子型和空穴型晶体管形成互补结构,从而获得高性能计算能力,但这种晶体管密度的提高主要是靠缩小单元晶体管的尺寸来实现。例如,大家最常见的案例就是半导体行业的高精度尺寸微缩,从 14>10nm>7nm>5nm(不代表实际栅距)这样一直按照 0.7 的倍率不断迭代。据复旦大学微电子学院官方公告,该学院教授周鹏、研究员包文中及信息科学与工程学院研究员万景团队绕过 EUV 工艺,研发出性能优异的异质 CFET 技术

- 关键字:

复旦大学 晶体管

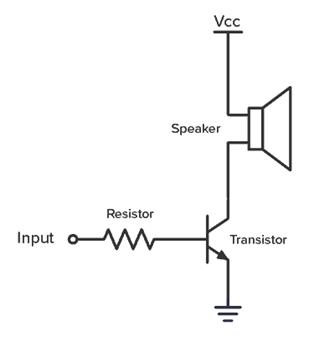

- 晶体管是一个简单的组件,可以使用它来构建许多有趣的电路。在本文中,将带你了解晶体管是如何工作的,以便你可以在后面的电路设计中使用它们。 一旦你了解了晶体管的基本知识,这其实是相当容易的。我们将集中讨论两个最常见的晶体管:BJT和MOSFET。 晶体管的工作原理就像电子开关,它可以打开和关闭电流。一个简单的思考方法就是把晶体管看作没有任何动作部件的开关,晶体管类似于继电器,因为你可以用它来打开或关闭一些东西。当然了晶体管也可以部分打开,这对于放大器的设计很有用。晶体管是一个简单的组件,可以使用它来构建许多有

- 关键字:

放大器 晶体管 MOS BJT

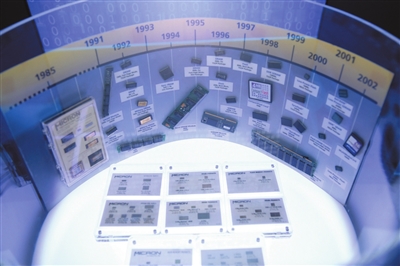

- 你知道吗?世界上第一个半导体晶体管并不是用硅材料做的,而是用一种叫作“锗”的稀有元素做的。在上世纪三四十年代初,使用半导体制作固态放大器的想法被陆续提出,第一个实验结果是由波欧与赫希完成的,使用的是溴化钾晶体与钨丝做成的闸极,虽然它的操作频率只有一赫兹,并无实际用途,却证明了类似真空管的固态三端子组件的实用性。 二战后,贝尔实验室提出想要做出固态放大器的目标,经过几位科学家的实验和改进,最终由巴丁和布莱登用涂蜡钨丝和硅制成第一个点接触电晶体,继而制作出第一个语音放大器。在这之后,萧克莱设想是否能使用

- 关键字:

半导体 晶体管 历史 博物馆

- 据东芝近日官网宣布,他们的第三代 SiC MOSFET(碳化硅场效应管)计划在今年 8 月下旬开始量产。据了解,该新产品使用全新的器件结构,具有低导通电阻,且开关损耗与第二代产品相比降低了约 20%。2020 年 8 月,东芝利用这项新技术量产了第二代 SiC MOSFET ——1.2kV SiC MOSFET。这是一种将 SBD 嵌入 MOSFET 的结构,将其与 PN 二极管 并联放置 ,能将可靠性提升 10 倍 。虽然上述器件结构可以显著提升可靠性,可它却有着无法规避的缺点 —— 特定导通电阻和性能

- 关键字:

东芝 半导体 场效应管

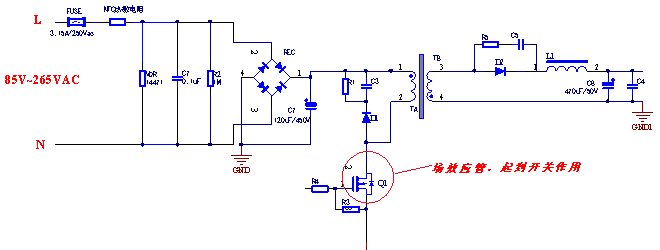

- 晶体管、MOS管、IGBT管是常见的电力电子控制器件。电流触发晶体管只能控制开启,不能控制关闭属于半可控件;电压触发MOS管、IGBT管既可以控制开启,也可以控制关断属于全可控件。搞懂控件的特点对电力电子器件维修尤为重要,小编根据所学及理解做如下总结,希望能给大家一些帮助。一、晶闸管 1、别名:可控硅是一种大功率半导体器件,常用做交流开关,触发电流>50毫安 2、特点:体积小、重量轻、无噪声、寿命长、容量大、耐高压、耐大电流、大功率 3、主要应用领域:整流、逆变、变频、斩波(直流-

- 关键字:

IGBT 晶体管 MOS管

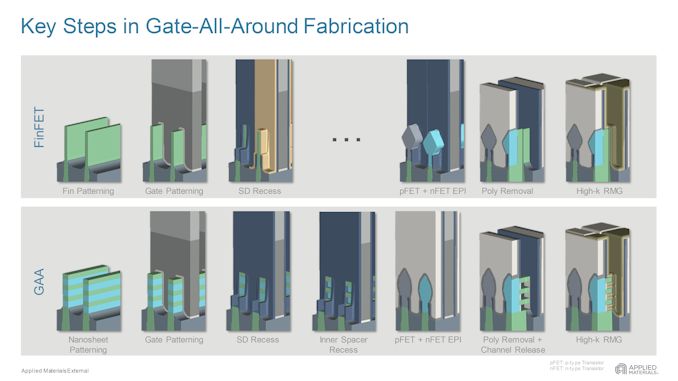

- 上月,三星代工(Samsung Foundry)部门悄然宣布,其定于 2022 年 2 季度开始使用 3GAE 技术工艺来生产芯片。作为业内首个采用 GAA 晶体管的 3nm 制程工艺,可知这一术语特指“3nm”、“环栅晶体管”、以及“早期”。不过想要高效地制造 GAA 晶体管,晶圆厂还必须装备全新的生产工具。 而来自应用材料(Applied Materials)公司的下一代工具,就将为包括三星在内的晶圆厂提供 GAA 芯片的制造支持。(来自:Applied Materials 官网 ,via

- 关键字:

3nm 晶体管

- 1、放大电路场效应管具有输入阻抗高、低噪声等特点,因此经常作为多级放大电流的输入级,与三极管一样,根据输入、输出回路公共端选择不同,将场效应管放电电路分为共源、公漏、共栅三种状态,如下图是场效应管共源放大电路,其中:Rg是栅极电阻,将Rs压降加至栅极;Rd是漏极电阻,将漏极电流转换成漏极电压,并影响放大倍数Au;Rs是源极电阻,为栅极提供偏压;C3是旁路电容,消除Rs对交流信号的衰减。2、电流源电路恒流源在计量测试应用很广泛,如下图是主要是由场效应管组成的恒流源电路,这是可作为磁电式仪表调标尺工序。由于场

- 关键字:

MOSFET MOS 场效应管

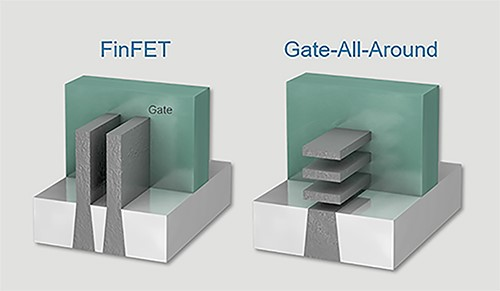

- 半导体设备大厂应用材料推出多项创新技术,协助客户运用极紫外光(EUV)持续进行2D微缩,并展示业界最完整的次世代3D环绕闸极(Gate-All-Around,GAA)晶体管制造技术组合。芯片制造商正试图透过两个可相互搭配的途径来增加未来几年的晶体管密度。一种是依循传统摩尔定律的2D微缩技术,使用EUV微影系统与材料工程以缩小线宽。另一种是使用设计技术优化(DTCO)与3D技术,巧妙地藉由优化逻辑单元布局来增加密度,而不需要改变微影间距。第二种方法需要使用晶背电源分配网络与环绕闸极晶体管,随着传统2D微缩技

- 关键字:

应用材料 EUV 2D微缩 3D环绕闸极 晶体管

- 据国外媒体报道,正如外媒此前所预期的一样,芯片代工商台积电在今日开始的全球技术论坛上,披露了下一代先进工艺3nm的更多细节信息。2020年的台积电全球技术论坛,是他们举行的第二十六届全球技术论坛,论坛上分享了第一代5nm、第二代5nm、4nm等先进工艺方面的信息,但在5nm工艺已经投产的情况下,外界最期待的还是5nm之后的下一个全新工艺节点3nm工艺。在今天的论坛上,台积电也披露了3nm工艺的相关信息。他们的3nm工艺,仍将继续使用鳍式场效应(FinFET)晶体管,不会采用三星计划在3nm工艺节点上使用的

- 关键字:

台积电 3nm 5nm 晶体管

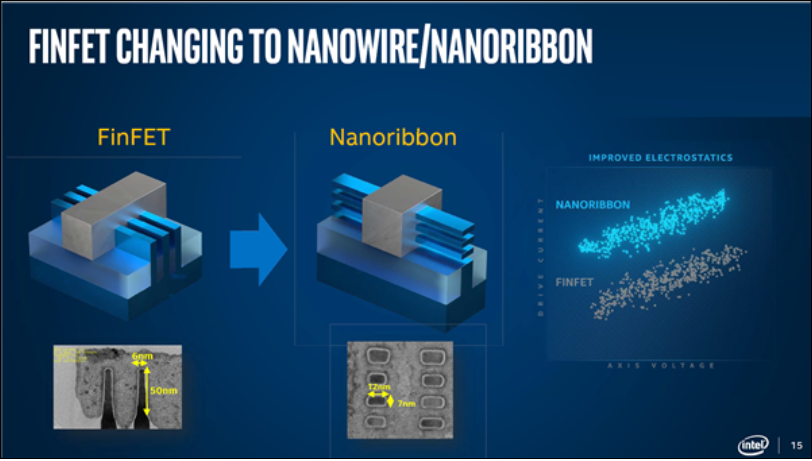

- Intel这几年虽然在制造工艺上步伐慢了很多,但是说起半导体前沿技术研究和储备,Intel的实力仍是行业数一数二的。在近日的国际超大规模集成电路会议上,Intel首席技术官、Intel实验室总监Mike Mayberry就畅谈了未来的晶体管结构研究,包括GAA环绕栅极、2D MBCFET多桥-通道场效应管纳米片结构,乃至最终摆脱CMOS。FinFET立体晶体管是Intel 22nm、台积电16nm、三星14nm工艺节点上引入的,仍在持续推进,而接下来最有希望的变革就是GAA环绕栅极结构,重新设计晶体管底层

- 关键字:

英特尔 CPU处理器 晶体管 3nm

- 近日,台积电正式披露了其最新3nm工艺的细节详情,其晶体管密度达到了破天荒的2.5亿/mm2!

- 关键字:

台积电 晶体管 3nm

晶体管-场效应管介绍

您好,目前还没有人创建词条晶体管-场效应管!

欢迎您创建该词条,阐述对晶体管-场效应管的理解,并与今后在此搜索晶体管-场效应管的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473