- 2023年ChatGPT引发的AI热潮仍在继续,近期媒体报道,今年拥有云端相关业务的企业,大多都向英伟达采购了大量GPU,目前该公司订单已排至2024年。同时,由于英伟达大量急单涌入,晶圆代工企业台积电也从中受益。据悉,英伟达正向台积电紧急追单,这也令台积电5纳米制程产能利用率推高至接近满载。台积电正以超级急件(superhotrun)生产英伟达H100、A100等产品,而且订单排至年底。业界认为,随着ChatGPT等AIGC(生成式人工智能)快速发展,未来市场对GPU的需求将不断上升,并将带动HBM以及

- 关键字:

AI GPU HBM 先进封装

- 2022 年到 2028 年先进封装市场年复合增长率将达 10.6%。

- 关键字:

先进封装 小芯片

- 近日,楷登电子(Cadence)宣布基于台积电3nm(N3E)工艺技术的Cadence® 16G UCIe™ 2.5D先进封装IP成功流片。该IP采用台积电3D Fabric™ CoWoS-S硅中介层技术实现,可提供超高的带宽密度、高效的低功耗性能和卓越的低延迟,非常适合需要极高算力的应用。据悉,楷登电子目前正与许多客户合作,来自N3E测试芯片流片的UCIe先进封装IP已开始发货并可供使用。这个预先验证的解决方案可以实现快速集成,为客户节省时间和精力。

- 关键字:

楷登电子 台积电 N3E UCIe 先进封装 IP

- 2022年12月,三星电子成立了先进封装(AVP)部门,负责封装技术和产品开发,目标是用先进的封装技术超越半导体的极限。而根据韩媒BusinessKorea最新报导,三星AVP业务副总裁暨团队负责人Kang

Moon-soo近日指出,三星将藉由AVP业务团队,创造现在世界上不存在的产品。报导指出,最先进的封装技术可藉由水平和垂直的方式,连接多个异质整合技术的半导体,使更多的电晶体能够整合到更小的半导体封装中,这方式提供了超越原有性能的强大功能。对此,Kang

Moon-soo指出,三星电子是世界上

- 关键字:

半导体 先进封装

- 作为一家专注提供高端芯片封测方案的服务商,锐杰微科技(RMT)主要聚焦复杂芯片的封装方案设计、规模化封装加工制造及成品测试,“我们的使命就是帮助国内高端核心芯片完成国产化封测。”锐杰微科技集团董事长方家恩如是说。 锐杰微科技的前身是成立于2011年的芯锐公司,主要提供高端芯片封装设计和仿真业务,2016年随着成都RMT成立并投产,开始转型提供高端SiP及处理器封装制造。此后的2019至2022年间,RMT郑州封测基地一期项目投产并展开二期布局、总部落户苏州、完成近3亿元B轮融资、筹划苏州封测基地

- 关键字:

锐杰微科技 先进封装 国产高端芯片

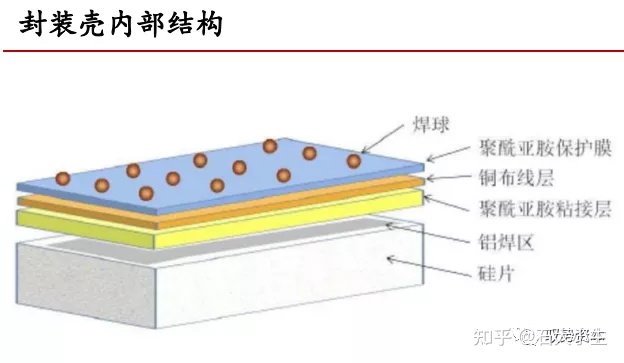

- 半导体制造的工艺过程由晶圆制造(Wafer Fabr ication)、晶圆测试(wafer Probe/Sorting)、芯片封装(Assemble)、测试(Test)以及后期的成品(Finish Goods)入库所组成。半导体器件制作工艺分为前道和后道工序,晶圆制造和测试被称为前道(Front End)工序,而芯片的封装、测试及成品入库则被称为后道(Back End)工序,前道和后道一般在不同的工厂分开处理。前道工序是从整块硅圆片入手经多次重复的制膜、氧化、扩散,包括照相制版和光刻等工序,制成三极管、

- 关键字:

芯片封装 半导体封装 先进封装 BGA WLP SiP 技术解析

- 7月14日消息,据台湾媒体报道,台积电冲刺先进制程的同时,正同步加大先进封装投资力度,并扶植弘塑、精测、万润及旺硅等设备、材料商,建构完整生态系,以绑住苹果等大客户订单。台积电台积电已宣布,今年资本支出达150亿美元至160亿美元,其中10%用于先进封装,同时,因应南科产能扩建,将在南科兴建3D封测新产线,并在龙潭、竹南持续扩充先进封测规模。台积电认为,进入5G时代之后,很多高速运算、车载芯片都需要5nm以下先进制程,甚至智能手机也整合AI及医疗诊断等强大功能的芯片,并利用先进封装技术,和其他不同的芯片堆

- 关键字:

台积电 先进封装 苹果

先进封装介绍

您好,目前还没有人创建词条先进封装!

欢迎您创建该词条,阐述对先进封装的理解,并与今后在此搜索先进封装的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473