在DDR3 SDRAM存储器接口中使用调平技术

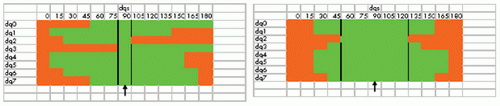

可以在运行时从FPGA架构访问延时单元,作为启动校准过程的一部分,实现自动DDR3去斜移算法。图6所示为怎样对DQ数据 去斜移,中心对齐DQS,提高采集余量。还可以利用输出延时在输出通道中插入少量的斜移,有意减少同时开关的I/O数量。

本文引用地址:https://www.eepw.com.cn/article/86471.htm

图6. DQS组中的DQ去斜移概念,以90度相移DQS为中心

可靠采集

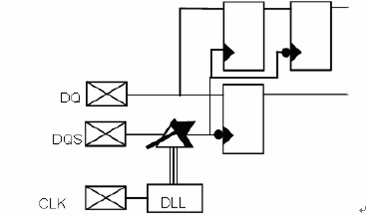

DQS信号起到输入选通的作用,必须移至合适的位置以采集读操作。相移电路(图7中所示)可以把到达DQS信号移相0°、22.5°、30°、36°、45°、60°、67.5°、72°、90°、108°、120°、135°、144°和180°,具体数值取决于DLL频率模式。移位后的DQS信号被用作I/O单元输入寄存器时钟。

图7. DQ采集电路

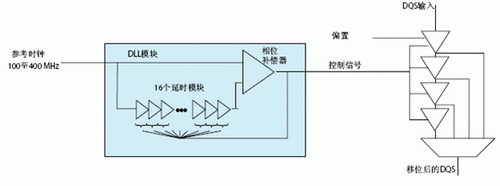

图7所示的延时锁定环(DLL)将PVT相移保持在固定位置。图8所示为DLL和相移电路之间的关系。

图8. DLL和DQS相移电路

DLL使用频率参考来动态产生每一DQS引脚的延时链控制信号,使其能够补偿PVT变化。Stratix III器件中有4个DLL,每个都位于器件的角上。每个DLL延伸到器件的两侧,使器件在所有侧面都实现了对多个DDR3 SDRAM存储器的接口支持。

高速数据速率域交叉和设计简化

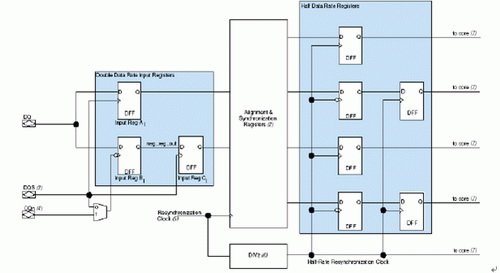

DDR采集寄存器和HDR寄存器使数据能够从双倍数据速率域(在时钟两个边沿的数据)安全下传至SDR域(同一时钟频率一个上升沿的数据,但数据宽度加倍),以及HDR域(时钟上升沿的数据,但是频率只有SDR的一半,数据宽度加倍),更容易达到内部设计时序。图9所示为DQ数据是怎样通过各种数据速率域的。

图9. Stratix III输入通道寄存器

提高管芯、封装和数字信号的完整性

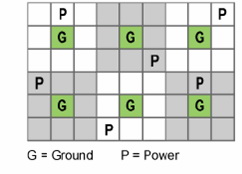

FPGA管芯和封装的设计应具有可靠的信号完整性,实现高性能存储器接口(即,有8:1:1用户I/O至地和电源比,以及较好的信号返回通道,如图10所示)。此外,设计还应具有OCT、可变摆率和可编程驱动能力,以便正确地控制信号质量。

图10. 每一电源和地的8个用户I/O

结论

高性能FPGA具有较宽的存储器带宽,增大了时序余量,能够灵活地进行系统设计,进一步完善了高性能DDR3 SDRAM DIMM。FPGA和DDR3 SDRAM相结合满足了当今通信、网络和数字信号处理系统的大吞吐量需求。

可控硅相关文章:可控硅工作原理

比较器相关文章:比较器工作原理

存储器相关文章:存储器原理

评论