基于FPGA状态机和片上总线的CompactPCI异步串口板设计方案

摘要:首先简要介绍了CompactPCI异步串口板的通常设计方法,并且提出了这些方法的不足之处,重点阐述了基于FPGA状态机和片上总线的新设计方案,以及该方案的技术优势,随后公布了基于该方案的异步串口板达到的性能指标。通过比较有关应答延迟的试验数据,提出了基于FPGA状态机和基于DSP处理器的异步串口板卡存在明显的处理速度差异问题,并基于两种设计方案,解释了形成差异的原因。最后提出了FPGA状态机对外部总线存储器或端口的访问管理性能大幅超越了任何一款DSP处理器的观点,并对同行提出了类似研发项目的设计建议。

本文引用地址:https://www.eepw.com.cn/article/248894.htm引言

CompactPCI异步串口板安装在工业计算机CompactPCI扩展槽内,可实现工业计算机与外围多路设备串口之间的异步串行通讯。异步串口板有多种设计方案,不同的设计方案决定了板卡具有不同的通讯性能和可靠性。根据任务要求,某重要设备的测试平台必须达到36路通道、11种通讯协议、波特率4/19.2/38.4/57.6/115.2(kbps)、小于1ms的处理时间、通讯模式可配置和高可靠性的试验要求,因此测试平台内异步串口板的设计方案要面向上述试验要求而制定。

1 背景技术

1.1 现有技术

目前CompactPCI异步串口板一般采用以下两类方法实现。

1.1.1 使用嵌入式处理器作数据处理单元

采用独立的嵌入式处理器作为数据处理单元,异步串口单元要么使用嵌入式处理器自身的2到3个异步串口,要么使用连接到FPGA片内总线的通用异步收发器或异步收发逻辑,从而建立起一主多从式总线结构。

1.1.2 使用FPGA芯片集成收发逻辑和处理逻辑

采用FPGA芯片集成了若干独立的异步串口通路,每个通路均有一对处理逻辑和收发逻辑,其中收发逻辑实现了一路串行数据的接受、发送和并串转换,处理逻辑实现了一路串行数据的读取、处理和存储。

2 设计方案

2.1 设计思路

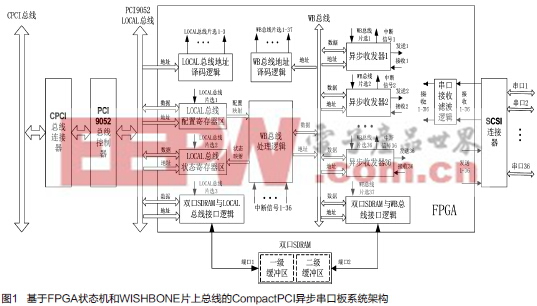

为便于性能比较,在采用第一类设计方案的总线式系统结构基础上,分别用TMS320C6416 DSP处理器和FPGA状态机作处理单元,实现了两块异步串口板(两者系统结构、程序流程、通讯功能和软硬件接口均相同)。每块均在FPGA片上总线集成了36个UART软核、1个双口SDRAM接口逻辑、地址译码器、配置状态寄存器区,以及串口接收滤波逻辑等,两者不同之处在于FPGA状态机作处理单元的串口板在FPGA上实现了一个完整的片上系统。下文重点介绍了后者的实现方法、性能指标,并对两者的处理速度进行了比较和分析。

2.2 实现方法

2.2.1 板卡设计

基于FPGA状态机和WISHBONE片上总线(图中简称为WB总线)的36通路CompactPCI异步串口板系统架构如图1所示。

fpga相关文章:fpga是什么

评论