基于FPGA状态机和片上总线的CompactPCI异步串口板设计方案

3 试验数据分析

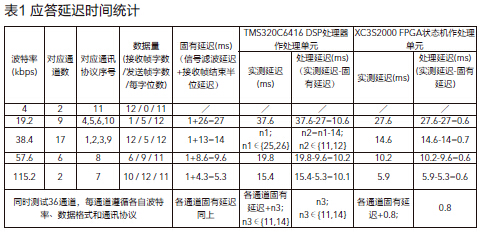

本文引用地址:https://www.eepw.com.cn/article/248894.htm在联机试验中,测试平台先后使用了由TMS320C6416 DSP处理器和XC3S2000 FPGA状态机作处理单元的异步串口板,分组测试了相同波特率的通道,及全部通道,通讯周期200ms,每通道间隔5ms。试验重点考察应答延迟时间,其由两部分组成,分别是固有延迟和处理延迟。其中固有延迟由为滤波设置的1ms滤波延迟和为判断接收帧结束而设置的半位延迟组成,半位延迟与波特率成反比。处理延迟由处理单元访问总线端口、数据处理和实现通讯协议所耗时间组成,实测应答延迟时间统计如表1所示。

从统计表得出如下结论。

(1)无论采用何种处理单元,处理延迟与波特率和通讯数据量无关。因为上位机已将数据写入各通道的数据发送子区,依据接收帧命令参数,DSP处理器和FPGA状态机只需进行简单逻辑和算法运算即可获得发送数据帧,对于4-115.2kbps之间的波特率和12字节的数据量,有充分时间裕量,不会出现处理瓶颈。

(2)TMS320C6416 DSP处理器作处理单元时,处理延迟及其变化范围较大,而且通道数越多,处理延迟及其变化范围越大,反之则越小。因为DSP处理器I/O端口数量有限,当串口通道数量较多时,DSP处理器要通过片上总线访问异步收发器、SDRAM,和相当数量的输入/输出端口,以便和上位机、FPGA交换数据和信号。为了及时传输这些信号,DSP处理器还需要以一定的频率巡检这些信号。另外DSP处理器所有处理过程都是顺序执行的,处理时间与程序语句数量成正比关系。

(3)XC3S2000 FPGA状态机作处理单元时,处理延迟及其变化范围很小,而且与通道数量无关。因为FPGA集成片上系统后,其状态机与其它片上逻辑之间的信号传输通过片内布线完成,而布线资源几乎不受限,不仅简化了处理单元的处理任务,而且保证了信号的实时传输,不必巡检端口。另外FPGA状态机不仅能够通过状态转移完成时序功能,而且能够通过并行处理完成算法功能,所以全部处理时间基本由访问总线端口的程序语句数量决定,与算法和通道数量几乎无关。

(4) FPGA状态机对外部总线或端口的访问管理性能大幅超越了TMS320C6416 DSP处理器,片上逻辑之间的信号实时传输能力也大幅超越了后者。而高性能DSP处理器仅在内存中运行程序时速度快,但在管理外部总线存储器或端口时,其优势无法发挥。

4 建议

建议同行在研制“具有高时序性能的、多外设接口的、功能单一的设备”时,参考上述基于FPGA状态机和片上总线的设计方案。

参考文献:

[1]詹必胜,吴斌方,杨光友.多路同步串口的FPGA传输实现[J].电子产品世界,2009(5):38-40

[2]Xilinx, Inc. Spartan-3 FPGA Family: Complete Datasheet[M].2004

[3]Opencores.WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores[M].Revision:B.3.2002

[4]Gorban J.UART IP Core[M].Revision: 0.6.2002

[5]孙进平,王俊,李伟,等.DSP/FPGA嵌入式实时处理技术及应用[M].北京:航空航天大学出版社,2011

fpga相关文章:fpga是什么

评论