多核DSP的BootLoader程序的实现

·粗略估计B核的BootLoader程序执行时间,在A核的有效程序代码前加一个延迟程序。

·在A核的有效程序代码前加入一个死循环程序,当B核BootLoader程序执行完后,B核通知A核,A核就跳出这个死循环程序,开始执行自己的有效代码。

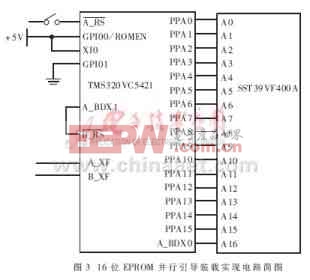

2.4 TMS320VC5421的16位并行EPROM工作方式的BootLoader程序的编程实现

首先设计一个简单的电路图,如图3所示。在DSP的A_XF和B_XF两个管脚分别连接一个发光二极管,A核以2Hz的频率点亮发光二极管,B核以10Hz的频率点亮发光二极管。将128K的FLASH(SST39VF400A)分成两页,每页为64K。FLASH的页的选择由TMS320VC5421的A_BDXO管脚控制。当A_BDX0为低电平,即FLASH的A16地址线为低电平时,选中FLASH的第一页,由FLASH的A0~A15地址线选择页内地址,用于存放A核的16位并行EPROM工作方式的Boot表。当A_BDX0为高电平,即FLASH的A16地址线为高电平时,选中FLASH的第二页,由FLASH的A0~A15地址线选择页内地址,用于存放B核的16位并行EPROM工作方式的Boot表。

CPU_A和CPU_B的程序流程图分别如图4和图5所示。

(1)片外总线冲突的解决

估算B核执行BootLoader程序所需的时间后,在A核的用户有效程序之前,加一段延迟程序。

延迟的时间计算如下:

TMS320VC5421DSP的DMA通道从片外数据空间读取一个字到片内数据空间,需要7个指令周期时间。

统计用户程序大小,将对应Boot表中的所有段的大小相加:N1+N2+...=N。

延迟的时间为N×7=7N个指令周期。

由上面所述的方法可知,只需在开始执行A核的有效程序之前加一段延迟7N个指令周期的代码即可。

(2)生成Boot表

对CPU_A来说,以A核程序流程图建立一个项目Ati.msk。产生Ati.out文件后,进入该目录的DOS环境,键入:

hex500 Ati.out-a-e 0x4000h-boot-bootorg PARALLEL-memwidth 16-romwidth 16-o Ati.hex

生成A核的16位并行EPROM工作方式的Boot表。

对CPU_B来说,同样以B核程序流程图建立一个项目Bti.msk。产生Bti.out文件后,进入该目录的DOS环境,键入:

hex500 Bti.out-a -e 0x4000h-boot-bootorg PARALLEL-memwidth 16-romwidth 16-o Bti.hex

生成B核的16位并行EPROM工作方式的Boot表。

在实现双核DSP的上电自举后,A核和B核的用户程序将会被存放在核内程序空间的不同页面上。如从DMA的角度观看:A核的用户程序将被存放在A核的程序空间的第0页上;B核的用户程序将被存放在B核的程序空间的第2页上。因此A核的Boot表不需要修改,而B核的Boot表中的所有存放页地址的表项中的内容要更改为2。

(3)FLASH编程实现

根据FLASH芯片的控制时序,编写一个简单的DSP程序,用于将A核的Boot表写入FLASH的低64K,将B核的Boot表写入FLASH的高64K。

3 上电试验结果

将电路上电后,A核控制的发光二极管开始闪烁,B核控制的发光二极管也开始闪烁,且A核发光二极管闪烁频率要低于B核发光二极管闪烁频率。由此现象可得出:A核与B核的BootLoader实现成功,未产生片外总线冲突;A核以2Hz的频率点亮发光二极管,B核以10Hz的频率点亮发光二极管。

评论