基于FPGA实现的SCI接口电路IP核的设计

仿真结果

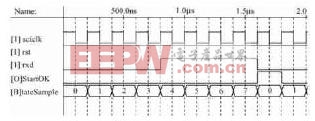

图6 起始位检测仿真波形

由图7仿真波形可知,采样一位数据的状态机在数据位的第4、5、6个内部sclk时钟进行。位值由多数采样的值决定,图中rxd在第4、5、6图7 采样一位数据的仿真波形个sclk时的值为1,故dok在第8个sclk时钟输出1,表示此次采样的一位数据为1。

图7 采样一位数据的仿真波形

结论

SCI接口电路由VerilogHDL语言描述,可读性好,便于修改与测试,可方便地嵌入到用户的FPGA系统。笔者利用Xilinx公司的Spartan ⅡFPGAXC2S100成功地实现了FPGA与PC机的串行通信。如在此基础上增加其它的控制寄存器,则可设计出功能更为完善的SCI接口电路。

评论