一种基于FPGA的复数浮点协方差矩阵实现

2.2 并行处理方案仿真结果

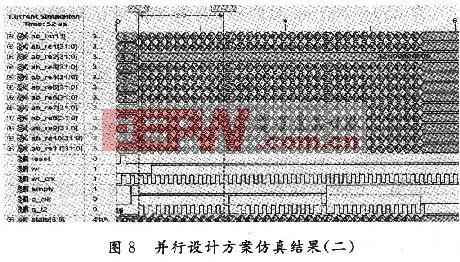

并行方案运算原理与串行方案的一样,只是在时钟控制上有所区别,因为采用了11个浮点复数乘累加器,进行一次矩阵运算,只需要11个时钟周期,如图7,图8所示。在仿真时,设置在写使能信号有效(wr=‘O’)的同时,有3个写时钟信号(wr_clk)的上升沿到来,即分别向22个FIF0中存入3个数据,则输出有3个矩阵。从图7中还可以清楚地看出,运算结果是矩阵的11行数据并行输出,输出结果是一个对称矩阵。

3 结语

在分析了目前应用于空间谱估计的协方差矩阵运算在硬件实现上的不足,如定点计算的数据动态范围小,运算精度不高,且只适用于特定阵列模型和的阵元数,不具备通用性。在此基础上提出了基于浮点运算的通用型协方差矩阵的实现方案。仿真结果表明,本文所提出的实现方案采用的是复数乘法运算,最终结果得到的是复共轭对称矩阵,适合利用任意的阵列模型和阵元数得到与之相对应的协方差矩阵。这就拓展了协方差矩阵运算的应用范围,且整个运算过程采用的是浮点运算,提高了整个运算的精度。

评论