一种基于FPGA的复数浮点协方差矩阵实现

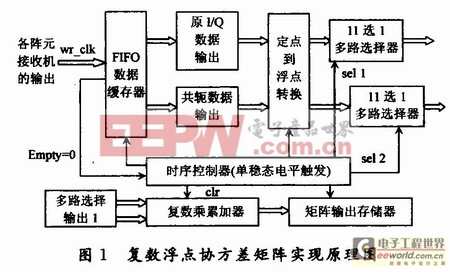

以11阵元的均匀圆阵为例,其协方差矩阵的求解方案原理框图如图1所示。

1.1 FIFO数据缓存器

在该设计方案中选择FIFO作为数据存储器,这是因为一旦多路接收机有数据输出,就会启动FIFO进行存储,进而FIFO的不空信号有效(empty=O),触发后续的矩阵运算;否则,运算停止,一切状态清零,FPGA恢复idle(空闲)状态,等待新的快拍采样数据的到来。

这样可以很方便地控制运算的开始和结束。矩阵运算所需要的同步时钟需要设计一个类似于单稳态触发器的模块。当检测到empty=‘0’时,就触发一个含有121个clk(对于串行方案而言)时钟信号周期长度的高电平。该高电平与主时钟相与便可以得到运算的同步时钟。

1.2 数据共轭转换

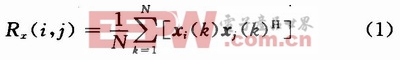

由于测向阵列的输出矢量X(t)是一个复矢量,对其求协方差矩阵需用阵列输出列矢量X(t)与其共轭转置矢量XH(n)对应相乘。如式(1)所示:

1.3 定点数到浮点数的转换

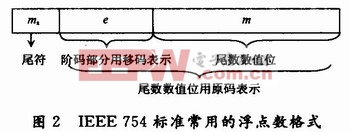

定点计算在硬件上实现简单,计算速度比浮点计算要快,但是表示操作数的动态范围受到限制,浮点数计算硬件实现比较困难;一次计算花费的时间也远大于定点计算的花费,但是其表示的操作数动态范围大,精度高。在本设计中,考虑到系统的数据动态范围和运算精度,选择浮点计算。由于运算数据是直接从接收机I,Q两路通道的A/D变换器的输出获得,为定点数,因此必须要有一个将A/D采样的定点数据转换为浮点数的过程。设计中将16位定点数转换为IEEE 754标准的单精度格式。32位单精度格式如图2所示,最高位为符号位,其后8位为指数e(用移码表示,基数f=2,偏移量为127),余下的23位为尾数m。

评论