一种基于FPGA的复数浮点协方差矩阵实现

1.4 浮点复数乘累加器

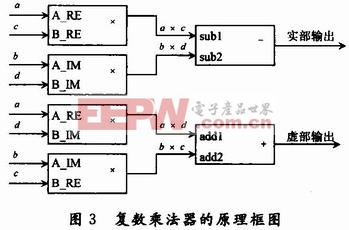

1.4.1 复数乘法器

假设有两个复数分别为a+jb和c+jd,这两个数的乘积为:

![]()

复数乘法器的工作原理如图3所示,其中所用到的加法、减法和乘法器都是基于浮点的运算。值得一提的是,在实现浮点加减法的时候,可以将尾数连同符号位转化为变形补码形式后再进行加减运算。这样做的目的是方便判断数据是否溢出(变形补码判断溢出的规则是:当两位符号位不同时表示溢出,否则无溢出。无论数据是否溢出,第一位符号位永远代表真正的符号),若溢出,则将尾数右归,指数部分加1,若没有溢出,则将尾数左归(规格化)。浮点乘法相对较简单,对应阶码相加,尾数相乘可以采用定点小数的任何一种乘法运算来完成,只是在限定只取一倍字长时,乘积的若干低位将会丢失,引入误差。

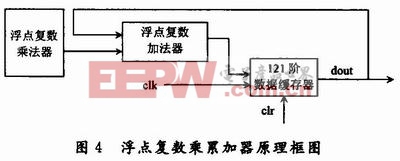

1.4.2 浮点复数乘累加器

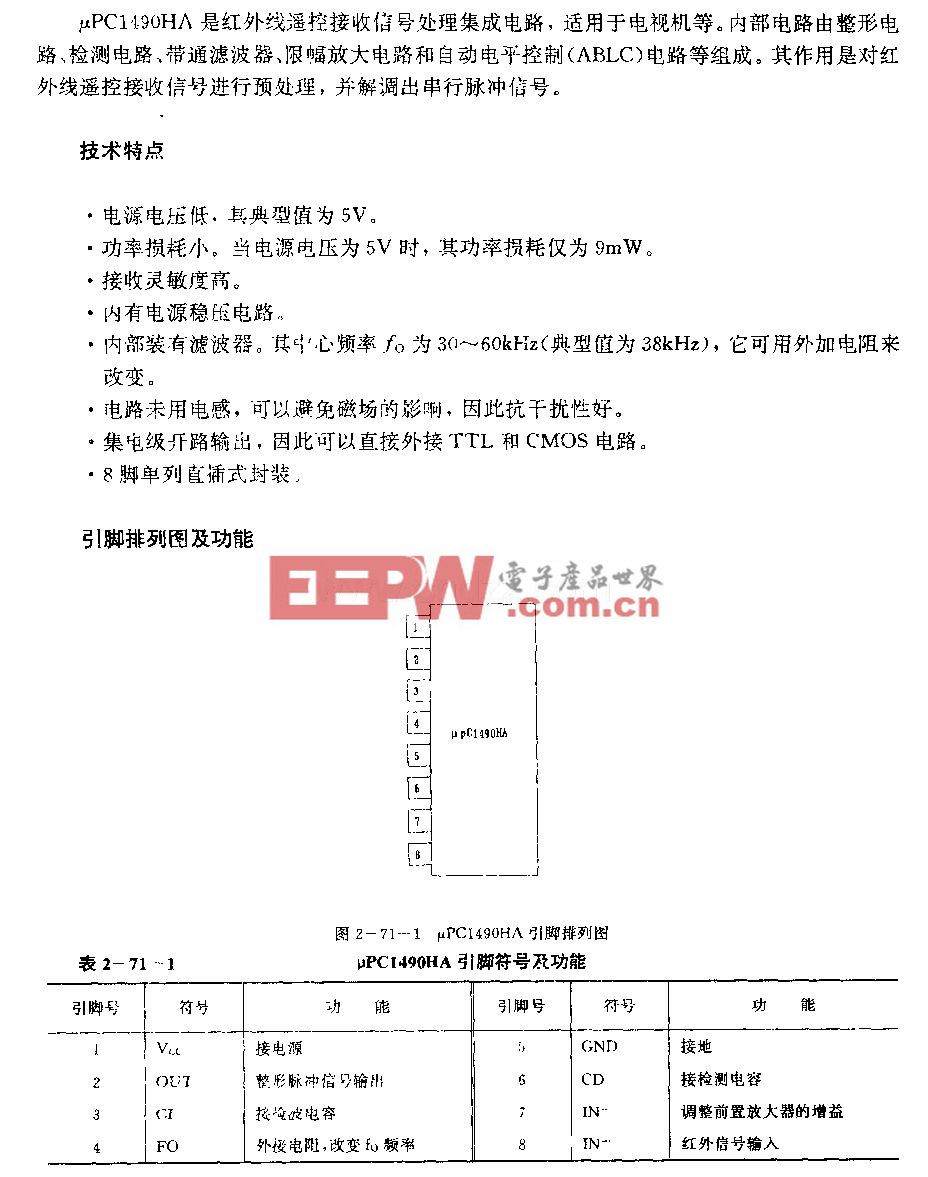

以11个阵元的圆阵为例,实现串行处理方案的浮点复数乘累加器的原理如图4所示,实部和虚部(双通道)的乘累加器模块工作原理一样。

121阶数据缓存器实际上就是121个数据锁存器级联形成的一个移位寄存器,初始状态为零。当浮点复数乘法器有输出的时候,启动数据缓存器与之进行加法操作,121个时钟周期以后可以实现一次快拍采样的矩阵累加。累加清零信号由时序控制器给出,当所有的快拍采样点运算都结束之后,数据缓存器输出累加结果(即协方差矩阵的运算结果),同时控制器送出一个清零信号,清零121阶数据缓存器。

评论