内存墙越筑越高

随着静态随机存取存储器(SRAM)在先进工艺节点下难以持续微缩,整个半导体行业必须评估其对各类计算场景的冲击,而短期内暂无简易解决方案。

核心要点

每一代工艺节点微缩时,同等容量的 SRAM 所占芯片面积比例持续上升。

该问题不仅局限于前沿 AI 芯片,最终将影响所有计算设备,甚至小型微控制器(MCU)与微处理器(MPU)。

行业可能需要进行架构变革;在逻辑芯片上堆叠 SRAM 小芯片可行,但成本高昂。

SRAM 是所有计算系统的核心组件,但其缩放进度已无法跟上逻辑电路的迭代速度,过去五年这一矛盾急剧恶化。

早在 1990 年,亨尼西与帕特森在《计算机架构:量化方法》一书中就明确指出:无论从容量还是性能来看,内存都将成为未来处理器发展的核心障碍。数十年来,硬件架构一直围绕这一难题优化,通常以 SRAM 作为高速缓存,搭配片外更大容量的动态随机存取存储器(DRAM)。这种方案让内存看起来更大,但速度往往慢得多,这就是著名的内存墙。

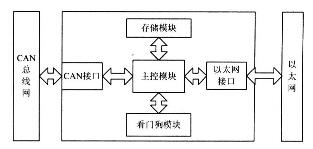

在所有计算场景中,程序与数据都存储在 SRAM 里,处理器从该内存读取指令,指令再指示处理器对同样存储于此的数据执行操作。

SRAM 比处理器内部暂存数据的寄存器更经济。尽管寄存器单元与 SRAM 使用的晶体管数量相当,但寄存器的解码与访问机制更昂贵,无法随寄存器组规模同步缩放。

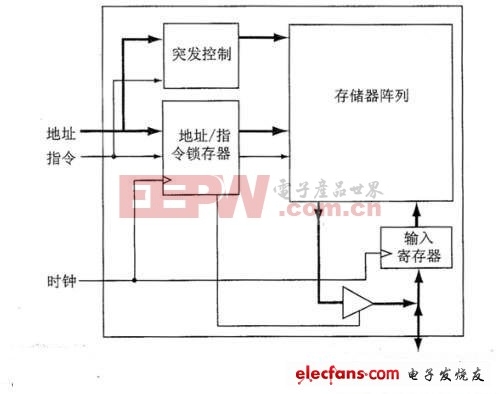

SRAM 由存储单元阵列与外围电路组成,支持数据随机读写。多数情况下,外围电路为半定制设计,会随内存阵列扩大而调整。事实上,内存速度的提升很多来自外围电路优化,而非存储阵列本身。

SRAM 的容量与性能提升已近乎停滞,前景愈发严峻。这意味着:每一代工艺节点微缩,同等容量 SRAM 占用的芯片面积占比不断攀升。当更多芯片达到掩模版极限时,无法承受这种面积开销,不得不更多依赖外部内存,而外部内存速度要慢数个数量级。

在 AI 时代,内存访问模式发生改变,内存墙迅速成为主要性能瓶颈。

台积电承认 SRAM 缩放存在问题,但该代工厂声称其全新 2 纳米纳米片技术已实现改进。不过,目前缺乏确凿数据支撑。以往经验显示,大规模商用前公布的指标,实际表现往往打折扣。

SRAM 缩放停滞

从逻辑上看,晶体管尺寸缩小,由 6 个晶体管构成的 SRAM 单元尺寸与性能也应同步提升。

新思科技嵌入式内存 IP 首席产品经理达里尔・塞策表示:SRAM 缩放停滞,源于经典 6T 位单元触及物理极限与工艺离散性限制。SRAM 位单元设计初衷是追求高密度,但存在读写需求冲突的固有缺陷:访问晶体管与存储晶体管相互制约,二者必须精细平衡并兼容工艺偏差。当几何尺寸持续缩小,偏差对位单元读写特性的影响占比显著放大。

问题不止于此。

Arteris 产品管理高级经理安德烈・博纳尔多指出:工艺节点微缩时,静电控制与随机离散性成为主导约束,阻止单元面积按比例缩小。此外,SRAM 速度已进入平台期,因为连线电阻与位线电容上升,而近期工艺节点的核心电压(Vdd)几乎未降低。逻辑电路可通过器件与布线创新持续缩放,但 SRAM 做不到。

在 2 纳米及更先进工艺上,SRAM 位单元缩放带来的密度提升已不足 15%,远低于 65 纳米到 5 纳米时代每代 50%–100% 的大幅微缩。这种下滑源于先进节点下器件、栅极接触、中层互连(MEOL)、V0/V1 线宽极窄,进一步有效缩放受限于设备与良率。

其直接后果是成本更高、性能更差。

Quadric 首席技术官奈杰尔・德雷戈表示:主要表现为内存密度缩放落后于逻辑电路,每平方毫米门数增长快于每平方毫米兆字节数。同时,线路延迟与物理定律导致访问速度下滑,不过智能架构调整可缓解逻辑电路与 SRAM 速度的依赖关系。

自上世纪 80 年代以来,内存与计算的差距持续扩大。如今计算机性能提升了近五个数量级,但内存带宽提升甚至不到 100 倍,处理器可处理的数据量与实际能获取的数据量之间存在超过 1000 倍的差距。

这不仅是前沿 AI 技术的问题,最终将影响所有设备,甚至小型 MCU 与 MPU,尤其随着 AI 向边缘渗透。

瑞萨电子首席产品营销经理卡维塔・查尔提到:当 SRAM 无法缩放,会占据更大的芯片面积比例,这必须纳入设计考量。同时影响芯片用户,他们需要权衡片内可实现功能与何时切换到外部内存,工艺越先进,成本越高。

关于 2 纳米节点的 SRAM 单元面积是否更优,行业尚无定论。

新思科技嵌入式内存 IP 高级产品经理拉胡尔・图克拉尔表示:近期 SRAM 的收益来自将逻辑微缩技术应用于 SRAM 宏的解码与控制电路,即便位单元未缩放,仍能通过设计创新实现面积优势。未来随着环绕栅极(GAA)技术成熟、器件宽度控制更灵活,有望进一步改善。GAA 晶体管静电控制更好,可降低漏电流、优化读写性能。2 纳米初期的内存面积提升,主要来自解码与数据通路电路中的逻辑器件优化;后续节点有望通过 GAA 晶体管实现位单元面积进一步缩小。

Arteris 的博纳尔多总结:SRAM 缩放放缓标志着系统架构进入拐点。当内存密度增长减速,单纯增加缓存容量在经济上不再高效。

对软件的影响

内存墙对软件的影响广泛,挑战了 “软件生产力是首要优化目标” 的长期理念。

依赖大量本地 SRAM 与多层高速缓存的处理器架构受冲击最大。通用 CPU 无法避开这种重硬件内存架构,因为手机、笔记本、数据中心的 CPU 需要运行随机用户代码,处理非结构化内存访问,同时调度数十个线程。

如今 SRAM 占据更大芯片面积与成本,大型寄存器文件与缓存层级不再免费缩放,给芯片面积、良率、能效与数据搬运效率带来压力。瓶颈从计算密度转向内存架构与互连效率。软件必须假设内存具有更强层级性、速度更不均匀,数据局部性、分块、分区、流量可预测性变得更重要,延迟波动成为系统级性能瓶颈。

AI 同样无法幸免。

随着 AI 模型规模与上下文长度增长,内存带宽与片上缓存成为性能主导因素,大语言模型推理中的 KV 缓存带宽瓶颈尤为明显。因此,软件必须优化数据局部性、内存感知调度、量化、稀疏性与内存分层,因为计算性能提升已无法弥补内存缩放缓慢的短板。

AI 架构存在可利用的差异:AI 引擎(尤其是推理处理器)可长时间处理结构化代码,远长于任务切换的 CPU。智能 AI 架构将内存管理交给离线编译器,由代码显式调度直接内存访问(DMA)传输模型权重与激活值,甚至可打造完全无需数据缓存的 AI 推理引擎,缓解对高速、高功耗 SRAM 的依赖。随着更多负载基于 AI 模型,先进 SoC 可在更大面积上避开 SRAM 密度与速度瓶颈,仅在关键 CPU 子模块保留该设计挑战。

近期 AI 模型的算术强度(处理器在内存数据上执行的运算量)持续下降,导致对内存到处理器的带宽需求更高。

3D SRAM 方案

若 SRAM 无法缩放,用最昂贵工艺制造它便失去意义。行业越来越倾向于将 SRAM 做成小芯片,堆叠在处理器上方。

SoC 设计师正在探索解耦方案:在先进工艺裸片上放置少量 SRAM,满足 CPU/GPU/AI 对 L1、L2 甚至 L3 缓存的核心需求;更大容量的 SRAM(如 L4)则放在上一代工艺裸片上,以获得更低的单晶体管成本。更快的裸片间互连与更精细的间距,让多层内存集成更简单,成本更低且延迟可接受。

但该方案目前成本高昂。

3D 与基于小芯片的 SRAM,因封装成本高、热设计复杂、标准化程度有限,目前仅在高端 AI / 高性能计算(HPC)芯片上具备经济性。面向低成本大众市场的 SRAM 小芯片,短期很难实现。

小芯片方案能以更低功耗提供数量级更高的带宽,是破除性能墙的关键,不仅是 2.5D,更是 3D 集成。

替代方案

每当内存出现问题,总会出现替代 SRAM 的新技术讨论。

新兴内存技术可在特定场景发挥作用,但无法全面替代 SRAM,未来多数系统将使用更多层级的内存,而非更少。

未来系统架构可能彻底改变。

内存内计算、近内存计算是 AI 推动的方向,意味着传统计算模型将发生变化。传统架构围绕巨型计算引擎搭建,需要从附近内存拉取数据。既然 SRAM 缩放已失效,行业将持续转向新型内存;更深层的问题是,现有 SRAM 使用方式是否已触及架构极限。Cerebras 的晶圆级引擎大幅增加片上内存,突破部分约束。

即便如此,单裸片能容纳的模型规模仍有上限,进而引出核心问题:单晶圆能高效完成多少任务? 若堆叠晶圆或扩大晶圆,架构能否良好缩放,还是最终遇到同样限制?

内存墙不是一次性障碍,若架构不变,模型每增大一级都会出现新壁垒。因此,设计决策必须聚焦系统可扩展性,从单裸片到多裸片,再到集群。最初是 CPU 集群,之后是小芯片集群,再到板级集群,如今扩展到整机柜作为统一计算资源。在纳米、毫米、厘米、米甚至公里级,每个阶段都会出现新挑战。最终,资源划分与管理方式决定能否突破反复出现的壁垒。

新型嵌入式内存正逐步落地。

例如,磁阻 RAM(MRAM)缩放性好、漏电流低、耐久性强,有望替代 SoC 中的部分嵌入式闪存与 SRAM;阻变 RAM(ReRAM)因集成容易、成本较低,在嵌入式非易失存储领域逐步普及。这些技术可补充但无法替代 L1/L2 缓存中的高性能 SRAM,但可替代部分控制器、MCU 与加速器中的嵌入式内存。

高带宽内存(HBM)显著提升 DRAM 带宽,由多层 DRAM 堆叠而成,底层传统上是面向处理器的裸片间物理层(PHY)。该基底裸片采用面向存储单元而非逻辑的工艺,受限于功率密度与热密度。若将基底裸片切换为逻辑优化工艺,可支持更多功能、提供更高性能。

这样可在 HBM 基底裸片与 GPU 之间实现更高带宽的裸片间接口,利用富余带宽连接更多 HBM,使 GPU 可访问的 HBM 容量翻倍,或用于 I/O 小芯片提供更高外部带宽,或二者结合。

在 SRAM 缩放不再自动受益的时代,架构效率(尤其是互连与一致性层面)成为每平方毫米性能与每瓦性能的核心杠杆。通过智能管理缓存布局与流量行为,缓存可在不按比例增加 SRAM 面积的前提下,获得足够的内存容量与带宽收益。

结论

内存墙越筑越高,短期看不到逆转迹象。SRAM 缩放不太可能重回往日势头,必须寻找替代方案。3D 堆叠将更普及,尤其在成本下降后,但没有万能解药。若高速内存成为计算瓶颈,计算架构必须更高效地利用现有内存。

评论