米尔ARM+FPGA架构开发板PCIE2SCREEN示例分析与测试

本次测试内容为基于ARM+FPGA架构的米尔MYD-JX8MMA7开发板其ARM端的测试例程pcie2screen并介绍一下FPGA端程序的修改。

本文引用地址:https://www.eepw.com.cn/article/202302/443693.htm01.测试例程pcie2screen

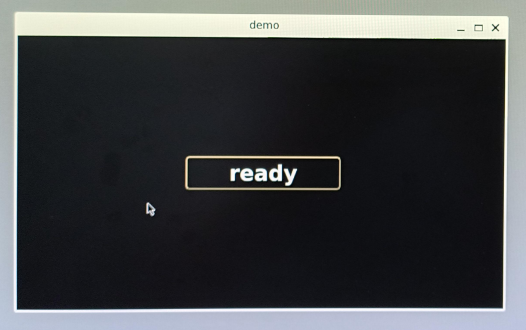

例程pcie2screen是配合MYD-JX8MMA7开发板所带的MYIR_PCIE_5T_CMOS 工程的测试例,它的作用是显示FPGA所连接的摄像头所采集的视频。运行该程序后屏幕会显示一个标题为demo的窗口。

使用鼠标点击 ready按钮,demo 窗口会显示连续的视频,说明摄像头、DDR、PCIE接口各部分正常。如果没有接摄像头,该程序会显示杂乱无章的图像。

该测试例的源码没有包括在SDK中,可以向米尔公司的技术人员索取。该实例程序是用Qt开发的,使用了OpenGL技术。程序包括以下几个主要的类:

● MainWindow:QMainWindow子类,是显示窗口的。

● uOpenglYuv:QOpenGLWidget子类,用于显示采集到的图像。该类的initializeGL函数用于初始化OpenGL。paintGL函数是用于绘制图像的,其中最核心的语句是:

glTexImage2D(GL_TEXTURE_2D, 0, GL_RGBA, vW, vH, 0, GL_RGBA, GL_UNSIGNED_BYTE, pRGB);

其中的pRGB保存从FPGA读取的数据。从这句我们可以看出该程序所要求的图像的格式。

● xdma_getImg:主线程类

● xdma_programe:对RIFFA接口进行了封装,其中的read_pack用于读取FPGA数据,被主线程循环调用。其函数定义如下:

int xdma_programe::read_pack(char *pData, int len)

{

//int buffer[1920 * 1080];

//int buffer[1024 * 768];

int buffer[1280 * 720];

int i;

if(dev_fd != NULL)

{

fpga_send(dev_fd, 0, buffer, len / 4, 0, 1, 25000);

fpga_recv(dev_fd, 0, buffer, len / 4, 25000);

memcpy(pData, (char *)buffer, len);

return len;

}

else

{

return 0;

}

}

从函数中可以看出,在每次读数据前,该函数先向FPGA写一次数据(数据无意义,和FPGA的状态机有关),每次读入一整帧的数据。

02.FPGA端程序的修改

FPGA端的逻辑控制在chnl_tester.v中,它定义了一个状态机,用于对数据收发进行控制。状态机定义如下:

always @(posedge CLK or posedge RST) begin

if (RST) begin

rLen <= #1 0;

rCount <= #1 0;

rState <= #1 0;

rData <= #1 0;

vout_vs_r <= #1 0;

end

else begin

case (rState)

3'd0: begin // Wait for start of RX, save length

if (CHNL_RX) begin

rLen <= #1 CHNL_RX_LEN;

rCount <= #1 0;

rState <= #1 3'd1;

end

end

3'd1: begin // Wait for last data in RX, save value

if (CHNL_RX_DATA_VALID) begin

rData <= #1 CHNL_RX_DATA;

rCount <= #1 rCount + (C_PCI_DATA_WIDTH/32);

end

if (rCount >= rLen)begin

rState <= #1 3'd2;

end

end

3'd2: begin // Prepare for TX

if (read_valid) begin

rCount <= #1 0;

rState <= #1 3'd3;

end

end

3'd3: begin // Start TX with save length and data value

if (CHNL_TX_DATA_REN) begin

//rData <= #1 data_in;

rCount <= #1 rCount + (C_PCI_DATA_WIDTH/32);

if (rCount >= rLen)

rState <= #1 3'd4;

end

end

3'd4: begin

if (vout_vs_r)

rState <= #1 3'd5;

else begin

vout_vs_r <= #1 1;

rState <= #1 3'd4;

rCount <= #1 0;

end

end

3'd5: begin

if (vs_flag) begin

rState <= #1 3'd0;

vout_vs_r <= #1 0;

end

else

rState <= #1 3'd5;

end

endcase

end

end

我们手头没有摄像头进行测试,所以简单修改该程序,使程序发送蓝色渐变色带信号。

核心修改如下:

……

reg [31:0] rColor = 0;

……

assign CHNL_TX_DATA = (read_en)? {rColor, rColor}:64'd0;

……

3'd3: begin // Start TX with save length and data value

if (CHNL_TX_DATA_REN) begin

//rData <= #1 data_in;

//if (rCount % 5 == 4)

rColor <= #1 rColor + 1;

if(rColor >= 255)

rColor <= #1 0;

rCount <= #1 rCount + (C_PCI_DATA_WIDTH/32);

if (rCount >= rLen)

rState <= #1 3'd4;

end

end

……

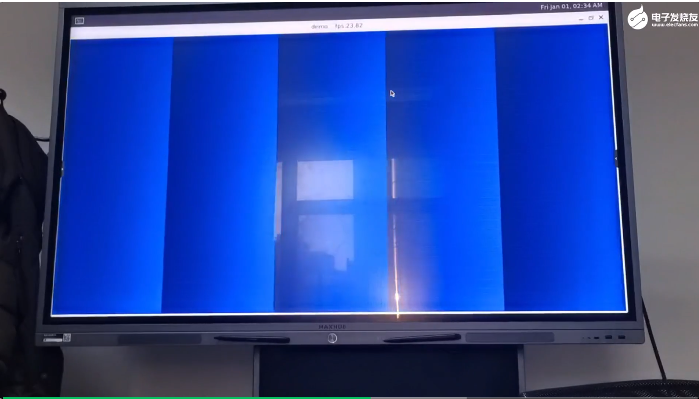

03.测试结果

我们没有修改ARM端的测试程序,仍然使用厂家提供的pcie2screen,只是重新烧写FPGA程序。程序的运行效果参见如下:

米尔MYC-JX8MMA7核心板及开发板。

米尔MYC-JX8MMA7核心板及开发板,采用ARM+FPGA的处理架构,采用NXP i.MX8M Mini及Xilinx Artix-7处理器,四核 Cortex-A53、Cortex-M4、Artix-7 CPU,1.8GHz主频,基于ARM+FPGA处理架构,具备高性能、低成本、低功耗等特点,两者各司其职,各自发挥原本架构的独特优势。搭载的Artix-7 CPU对标Zynq 7010的FPGA资源,能够满足高速数据采集的需求,并且采用PCIE高速通信,支持200~300MB/S的通信能力。能够提供出色的视频和音频体验,将媒体的特定功能与针对低功耗优化的高性能处理相结合,具备1080p 60Hz的H.265和VP9解码器,满足高清显示的要求。

为了方便开发者研究评估,米尔提供配套MYD-JX8MMA7开发板,采用12V/2A直流供电,搭载了1路千兆以太网接口、2路SFP光模块接口、1路USB2.0协议M.2 B型插座的5G模块接口、1路SDIO/串口协议的WIFI/蓝牙接口、1路HDMI显示接口、1路LVDS显示接口、1路MIPI CSI接口、1路DVP摄像头接口、1路音频输入输出接口、2路USB HOST Type A、1路USB Type-C、2路Micro SD、1路FMC扩展接口、1路兼容树莓派扩展模块接口。

关于米尔,领先的嵌入式处理器模组厂商。

评论