基于FPGA的图像裁剪电路的设计与实现

2.2.2 双端口RAM控制模块

VGA显示器要求行像素读取和显示同步,由于抽取出来的行列像素在时序上是不连续的,电路必须加存储器对提取的像素进行缓存。数据缓存模块可以选用任何存储单元,根据像素存取的特点,本设计选用了双端口的RAM对有效像素进行乒乓操作。双端口RAM乒乓操作的原理如图3所示。本文引用地址:https://www.eepw.com.cn/article/191745.htm

在第N个周期,将输入的数据流缓存到“数据缓存模块1”,与此同时,“数据缓存模块2”中缓存的数据通过“输出数据流选择单元”的选择,送到显示电路。在第N+1个周期,将输入的数据流缓存到“数据缓存模块2”,与此同时,“数据缓存模块l”中缓存的数据通过“输出数据流选择单元”的切换,送到显示电路。乒乓操作的最大特点是:通过“输入数据流选择单元”和“输出数据流选择单元”按节拍相互配合切换,将经过缓存的数据流没有时间停顿地传送到输出端,因此非常适合对时序不连续的像素进行流水线式处理。

根据双口RAM乒乓操作的原理,被抽取出来的像素,一行被缓存的同时,另一行则被顺序地读取出来,保证了像素显示的连续与同步。双端口RAM的输入输出信号的端口程序如下:

WIRE [29:0] DATA a,DATA b;

WIRE I_a=I;

WIRE I_b=~I;

WIRE[9:0]COIANTER a=(I)?ADDRESSl:COUNlER;

WIRE[9:0]COUNTER b=(!I)?ADDRESSl:COUNTER;

RAM U2(

.DATA a (INDATA),

.WREN a (I a),

.ADDRESS a(COUNTER a),

.CLOCK A(CLK),

.Q a(DATA a),

.DATA b (INDATA),

.WREN b(I_b),

.ADDRESS b(COUNTER b,

.CLOCK B (CLK),

.Q_b(DATA_b));

2.3 VGA显示控制模块

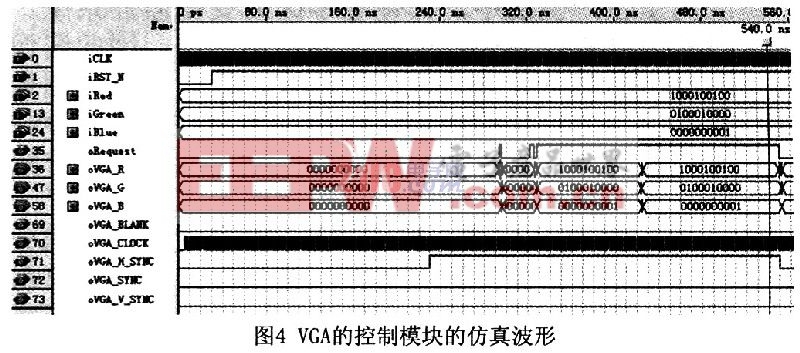

显示控制器主要用于输出VGA显示器所需要的RGB数据信号和控制信号,根据输入时钟,显示控制器可以产生VGA所需要的控制信号,包括场同步、行同步和复合消隐信号等。输出像素则与输入像素相同。图4为VGA的控制模块的仿真波形。

3 电路调试结果与分析

图5是分辨率为640×480的原图像,图6是分辨率为320×240,比例为4:3的图像。从处理后的图像效果可以看出,图像清晰,信息量丰富,能够满足图像的一般要求。

4 结论

本论文提出了一种基于FPGA的图像裁剪电路的设计方法,通过改变图像的分辨率达到压缩图像的效果。这种设计方法不仅具备了FPGA开发电路所具有的开发周期短、设计效率高、扩展性和升级性良好、设计灵活等特点,而且与通常所用的插值算法相比,电路结构简单、设计简便,从测试的效果来看,图像清晰,能够满足一般图像的要求。

DIY机械键盘相关社区:机械键盘DIY

评论