基于FPGA的图像裁剪电路的设计与实现

2 设计实现

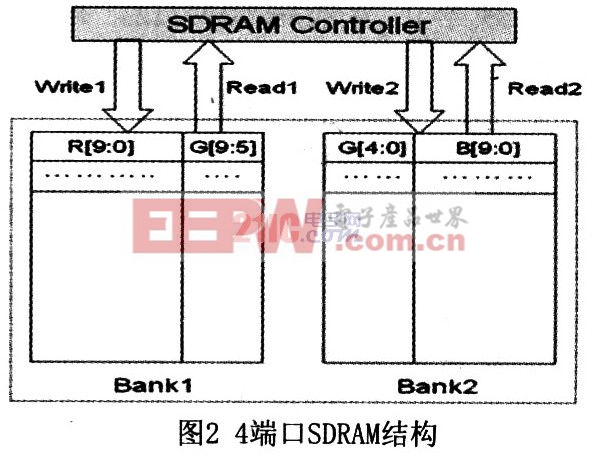

2.1 SDRAM控制模块的设计

预处理的图像需要放在存储器中,对于大部分的FPGA来说器件内部都含有4k的内存,但考虑到图像的容量及今后对动态图像处理功能的扩展,本设计选用了存储容量为8M外存的SDRAM。8M的SDRAM在存储空间上划分了4个BANK区块,每个BANK有16位数据宽。SDRAM虽然存储的容量大,但是其内部结构复杂,对该器件的读写使用必须设计专门的控制器进行控制操作。由于本设计采用的图像色彩为30位,RGB各10位,显然用一个16位宽度BANK不能存储一个像素,因此采用了2个BANK合并存储像素,如图2。这样一来,在SDRAM控制电路上需要仿真成四个虚拟的数据端口(两个写端口+两个读端口),在同一时刻将一个像素RGB从两个BANK中同时写入或读出,合并之后形成一个完整的数据。

根据这样的存取原则,一个具有640×480个像素、色彩为30位的图像,就需要同时BANKl和BANK2中存入640×480个16位的信息,SDRAM控制模块读入数据的端口程序如下所示,读出数据同理。

SDRAM_Control_4PortSDRAM0(

.WRl_DATA({R[9:0],G[9:5]}),

.WRl(E N),

.WRl_ADDR(0),----BANKl的地址

.WRl_MAX_ADDR(640*480),

.WRl_LENGTH(9'h100),

.WRl_LOAD(RST_0),

.WR1_CLK(P1X_CLK),

.WR2_DATA({G[4:0],B[9:0]}),

.WR2(E N),

.WR2_MAX_ADDR(22'h100000+640*480),

.WR2_LENGTH(9'hl00),

.WR2_LOAD(RST_0),

.WR2_CLK(PIX_CLK);

2.2 图像裁剪模块

在图像的裁剪处理上,有两种方案可选,第一种为线性插值算法。这是一种广泛使用的图像插值算法,通常使用8邻域采样加权产生新像素:

![]()

第二种为抽取算法,即通过变换分辨率的方法实现,例如将原来的640×480的分辨率变换为320×240或120×60的分辨率,这样图像的宽高比近似为4:3或16:8。比较两种算法,第二种算法通过直接丢弃部分原始数据达到分辨率的压缩,虽然有图像信息损失,但在图像显示满足要求的前提下,这种电路的实现更加便捷、方便,因此本设计采用了第二种算法。

2.2.1 像素的抽取

根据VGA的显示原理,储存在SDRAM中的640×480个像素,受显示控制电路中行同步信号的控制,每个行周期读出640个像素,并同步显示。采用抽取法实现分辨率的压缩,必须丢弃行和列的部分像素。以变换320×240分辨率为例,具体的设计方法是,将分辨率为640×480的原图像每隔一行进行行标记,在标记的行里,每隔1个像素进行列标记,最后将行列都被标记过的像素取出,提供给显示控制电路。

由于SDRAM存储器本身具有逐行读取、读取显示同步的特点,为了达到对行像素的隔行提取,本设计采用快读慢显的方式。例如原640× 480的分辨率采用25MHz的频率作为SDRAM数据读取频率和VGA的像素显示频率,现在采用50MHz作为SDRAM数据读取频率,VGA的像素显示频率仍然采用25MHz,即读取两行,保存一行并显示。在提取的行像素里每隔1个像素对列像素进行提取,则得到所需要的行列像素。

DIY机械键盘相关社区:机械键盘DIY

评论