基于FPGA的PCI硬件加解密卡设计

2.4 USB接口模块设计

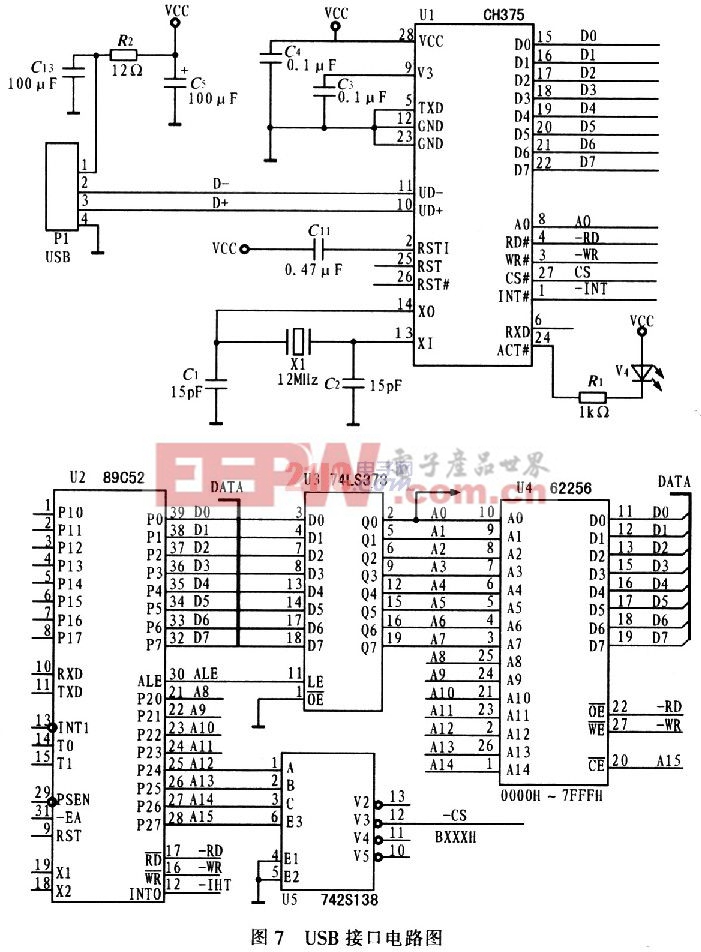

本系统的USB选用CH375B,工作于USB-HOST主机方式,采用并行接口。在USB主机方式下,CH375B支持各种常用的USB全速设备,外部单片机需要编写固件程序按照相应的USB协议与USB设备通讯。USB接口模块电路图如图7所示。本文引用地址:https://www.eepw.com.cn/article/191636.htm

CH375B并行接口信号线包括:8位双向数据总线D7~DO、读选通输入引脚RD#、写选通输入引脚WR#、片选输入引脚CS#、中断输出引脚INT#以及地址输入引脚A0。CH375B的RD#和WR#可以分别连接到单片机的读选通输出引脚和写选通输出引脚,CS#由地址译码电路驱动,INT#输出的中断请求是低电平有效,可以连接到单片机的中断输入引脚,单片机使用中断方式获知中断请求。当WR#为高电平并且CS#和RD#及A0都为低电平时,CH375B中的数据通过D7~DO输出;当RD#为高电平并且CS#和wR#以及A0都为低电平时,D7~DO上的数据被写入CH375B中;当RD#为高电平并且CS#和WR#都为低电平而AO为高电平时,D7~DO上的数据被作为命令码写入CH375B中。

3 软件的设计与实现

软件主要分为驱动程序和应用程序两部分,分别用DriverStudio和Visual C++开发。驱动程序的设计关键是如何完成硬件操作。基本功能包括设备的初始化、IO端口的读写操作、内存读写操作、中断的设置响应和调用等部分。PCI卡插入主机时,从设备中读出产品ID(PlD)和厂商ID(VID),由这2个值来搜索匹配的inf文件,再由inf文件加载相应的驱动。应用程序通过调用Win32 API函数CreatFile来打开设备,然后使用DeviceloControl与驱动程序通信。在应用程序退出前使用CloseHandle关闭设备。DeviceIoControl使用不同的IOCTL命令来调用驱动程序完成不同的任务。

4 结束语

经测试,本PCI加解密卡数据加密存储速度为612 KByte/s,解密读取速度为630 KByte/s。FPGA使用情况:total logicelements 903l/12060(75%),total pin 84/173(49%)。在以后的设计中,应重点解决系统加解密速度较慢的问题,另外,FPGA和USB的选型、加解密算法的优化等有待改进。

本设计的创新点在于用硬件加解密方法取代了通常的软件加解密方法,采用更为安全可靠的DESX算法来弥补DES算法的不足,使用了FPGA的IP软核设计方法实现DESX加解密模块和PCI接口模块,提高了系统集成度,可移植性好,便于系统升级。在加解密速度方面,用逻辑综合式取代时钟驱动级联式,使加解密一组数据的时间由16个周期缩短为1个周期。本系统在需要高级保密的商业和军事领域,有着较好的应用前景。

超级电容器相关文章:超级电容器原理

评论