FPGA实现UART和MCU一体化设计

2.1.2 输入/输出缓冲区(FIFC))的设计与实现

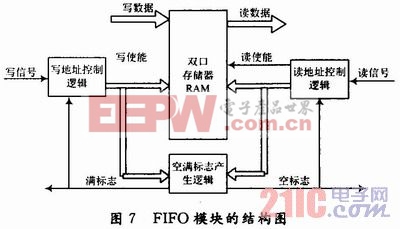

FIFO(First In First Out)是一种先进先出的缓冲区结构。主要在通信过程中解决通信两端速度不匹配的问题。访问FIFO仅需要读/写控制线,不需要地址线,因此采用FIFO实现的缓冲区接口简单,读写方便。由于文中的微控制器MCU和I/O设备均在FPGA内部实现,因此采用同步FIFO实现,即写端口和读端口采用同一个时钟进行控制操作。该系统分别实现了位宽为8位,深度为256 b的缓冲区来对MCU发送给外设的数据和从外设接收的数据进行缓冲处理。实现方法可以采用Altera公司FPGA内部的资源实现。对FIFO的读/写控制可根据缓冲区的使用状态和MCU发送来的命令来实现。FIFO模块的结构图如图7所示。本文引用地址:https://www.eepw.com.cn/article/191268.htm

读信号和写信号由微控制器MCU通过向I/O设备进行数据输入和输出操作产生。空标志和满标志用于MCU探测缓冲区状态,应用查询方式对外设进行读写数据操作。对于发送缓冲区,当缓冲区处于满状态时表明已经没有可用的存储空间缓冲数据,此时不允许进行写操作;对于接收缓冲区,当缓冲区处于空状态时,表明没有从设备收到任何的时间,此时不允许微控制器MCU从外设接收缓冲区读取数据。

通过QuartusⅡ产生的FIFO如图8所示。

图8中,aclr是异步复位信号;clock是时钟输入;rdreq和wrreq分别是读和写信号线;data[7…O]是FIFO的并行数据输入端;q[7…0]是FIFO的并行数据输出端;empty和full分别为FIFO空满标志的状态线;usedw[7…O]为当前状态下FIFO已经使用的存储量,即FIFO中已经写入并保存的数据量。

2.2 微控制器MCU的设计与实现

在一个计算机系统中,中央处理器处于核心控制地位,它不仅是参与运算的核心器件,而且是控制外设的中枢。一般情况下,它实现了一定的功能指令集,用来由用户自己编程控制外部设备动作或者进行一些算术逻辑运算。本文中所实砚的微控制器MCU主要以实现对外设的控制,实现了对外设端口的读写控制以及一些必要的程序控制指令。在一个微控制器的设计中,指令系统的设计尤其重要,它不仅关系到控制器的设计,也关系到软件程序的设计方法。指令系统的设计分为指令集设计和指令动作设计两部分,前者侧重于控制器的总体功能;后者侧重于指令的具体实现。进行指令设计时首先要进行指令分析,根据系统所要完成的功能,完成所需指令的功能设想,这是指令设计的基础;然后分析指令该放在什么地方,微控制器如何取指令和对指令进行识别等操作;最后确定指令格式以及每个指令完成指定功能所需要的一系列基本动作过程。可以使用ALtera公司FPGA内部的ROM作为程序存储器,详细的实现过程参看参考文献。通过此系统进行分析,设计实现如表1所示指令。每条指令功能的完成具有取指令、指令译码、执行指令阶段。指令的分析译码执行由状态机逻辑控制具体实现。

评论