基于NAND FLASH的高速大容量存储系统设计

3 系统设计

3.1 系统硬件结构组成

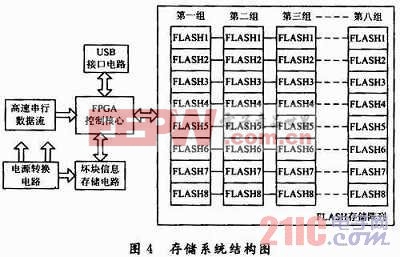

本文所设计的高速大容量存储系统的结构框图如图4所示。系统中FLASH芯片选用三星公司的K9WBG08U1M,存储阵列分为8组,采用流水线操作,每组由8片FLASH并联共用控制线,各组对应行的FLASH共用数据线。系统存储容量达到4×8×8=256 GB,存储速度理论值为40MB/ s×8=320 MB/s。FPGA是整个系统的控制核心,它将产生各种复杂的逻辑时序来控制外围芯片协调有序地工作,选用Altera公司StratixⅡ系列的EP2S60F484I4芯片,该芯片有48 352个逻辑单元,内置存储RAM容量达2.5 MB,满足缓存数据的要求。USB接口电路选用CYPRESS公司的CY7C68013A,该芯片集成了一个8.5 KB片上RAM的8051核、4 KB的FIFO以及USB 2.0收发器,满足USB2.0通信协议,是进行USB2.0开发的常用芯片。坏块信息存储电路用于存储和更新FLASH存储阵列随机出现的坏块位置,它必须是非易失零出错的存储介质,因此选用AMD公司的Am29LV800B NOR型FLASH,存储容量为8 Mb,保证无坏块。本文引用地址:https://www.eepw.com.cn/article/191199.htm

3.2 系统具体实现

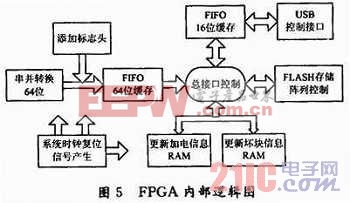

FPGA是整个硬件系统的核心,它完成电路的复杂时序控制,使系统有条不紊地运行。FPGA上电后进行初始化和加载配置信息,完成后进入工作状态。首先根据USB接口电压判断是进入数据记录状态还是数据下载状态,然后分别按照各自流程进行工作。FPGA内部逻辑设计如图5所示。

由于FLASH存储阵列是8片并联一起操作,因此数据总线宽度便为64位,同时由于USB的接口数据宽度为16位,因此系统中使用了2个FIFO分别进行缓存。在系统记录状态下,前端接收到高速串行数据后首先进行串/并转换,然后为其添加一个64位的标志头一并存入FIFO缓存,标识头是用来标记每次的加电情况,方便FLASH数据的分段下载。同时将外部NORFLASH内所存储的坏块信息读入FPGA内部建立的RAM中,在总接口控制下,屏蔽FLASH存储阵列内部的坏块,并按一定顺序将数据写入FLASH芯片。由于数据在存储过程中会产生新的坏块,因此在每页写操作结束后需判断此页编程是否成功,若编程失败,则对照此坏块地址更新RAM中的坏块信息,等待FLASH的存储操作结束后,再将更新后的RAM数据写入外部NOR FLASH进行保存。

在系统下载状态时,首先对FLASH内部的存储数据进行搜索,找到标识头所在存储阵列中的位置并将此位置信息写入FPGA内部的RAM中,这样便可知道每次加电后存储数据在FLASH阵列中的起始块位置和所占块的容量。然后通过上位机软件输入起始位置,块容量和下载命令后,FPGA内部的总接口控制便可根据这些命令信息,同时屏蔽坏块后将FLASH存储阵列中相应的数据写入16位FIFO缓存中,随后便可通过USB接口下载至计算机进行数据分析。

4 结语

随着基于NAND技术的FLASH固态存储器的快速发展,其存储密度也越来越大,而体积、功耗和成本却在减小,这使得NAND型FLASH在大容量高速存储设备的研制中得到广泛应用。本文针对单片FLASH存储速度慢的缺点,将多片低速FLASH芯片并行起来工作,同时又运用流水线操作节省了FLASH的自身编程时间,从而使得整个存储系统的存储速度大大提高。针对NAND FLASH内部存在坏块的问题,建立了一套完善的坏块处理机制,使得系统能够准确的存储数据,保证数据的可靠性。使用FPGA对FLASH存储阵列及USB下载电路进行控制,充分发挥了FPGA处理复杂逻辑的特点,简化了系统的硬件结构。

评论