基于FPGA的VGA可移植模块终极设计

c) 场同步信号设计

同上。

d) 数据显示坐标以及输出设计

//------------------------------------------

assign vga_xpos = (hcnt H_DISP) ? hcnt[9:0]+1'b1 : 10'd0;

assign vga_ypos = (vcnt V_DISP) ? vcnt[9:0]+1'b1 : 10'd0;

assign vga_rgb = ((hcnt H_DISP) (vcnt V_DISP)) ? vga_data : 16'd0;

这部分很容易理解,在显示期坐标根据显示的扫描而改变,在非显示期,坐标置零。

(2)Vga_display.v代码分析

a) 标准色彩定义

//define colors RGB--5|6|5

localparam RED = 16'hF800;

localparam GREEN = 16'h07E0;

localparam BLUE = 16'h001F;

localparam WHITE = 16'hFFFF;

localparam BLACK = 16'h0000;

localparam YELLOW = 16'hFFE0;

localparam CYAN = 16'hF81F;

localparam ROYAL = 16'h07FF;

定义当地的参数,目的是为了后续标准色彩调用的方便,没有其他作用。

b) 根据固定区域输出数据

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

vga_data = 16'h0;

else

begin

if (vga_xpos >= 0 vga_xpos (H_DISP/3))

vga_data = RED;

else if(vga_xpos >= (H_DISP>>3)*1 vga_xpos (H_DISP/3)*2)

vga_data = GREEN;

else

vga_data = BLUE;

end

end

如上代码,根据xpos坐标,来输出固定色彩。由于vga_driver模块已经完全设计好接口,因此vga_display.v模块就是简单的根据区域,输出设计的颜色。

(3) Vga_ctrl.v代码分析

a) 同步化解析

略。

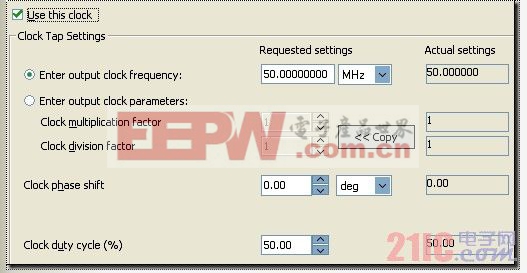

b) 可控锁相环PLL设计

本来可空锁相环PLL设计,Bingo想单独成章来讲述的,但觉得可能别的地方实际应用价值不是很大,最后便在此处阐明这样设计的原因。

由于VGA不同分辨率的扫描时钟不同,因此分辨率变化的时候,PLL的输出时钟是必要跟随着变化。但是Bingo觉得好麻烦,于是想了偷懒的一招:PLL IP定义,无非是用Quartus II GUI对PLL参数的设定,最后生成pll.v这个文件。而这个文件相当于是锁相环的驱动电路,故势必包含着参数的定义。实际如下:

altpll_component.clk0_divide_by = 1,

altpll_component.clk0_duty_cycle = 50,

altpll_component.clk0_multiply_by = 1,

如上图所示,每次修改参数,这三个变量会相应的发生变化。因此,何不把这三个参数作为例化的参数,可以再顶层直接修改代码来实现固定频率的输出?这样岂不是很方便?

因此设计参数例化接口如下:

#(

parameter DUTY_CYCLE = 50,

parameter DIVIDE_DATA = 1,

parameter MULTIPLY_DATA = 1

)

理论上是完全行得通的,这样设计的另一个好处就是电路的封装性更好Bingo实践证明,完全可行,因此在此处说明,要学会正确的偷懒呵呵。

(4)Vga_design.v顶层文件代码解析

a) Vga接口定义

//vga interface

output vga_adv_clk,

output vga_blank_n,

output vga_sync_n,

output vga_hs,

output vga_vs,

output [15:0] vga_rgb

如上所示,上面三个信号线是在使用adv712x视频转换芯片的时候才会出现,一般的电阻模拟电路,或者直接RGB3线驱动,可以直接删除相关信号以及电路。

评论