基于FPGA的VGA可移植模块终极设计

b) 专用视频转换芯片

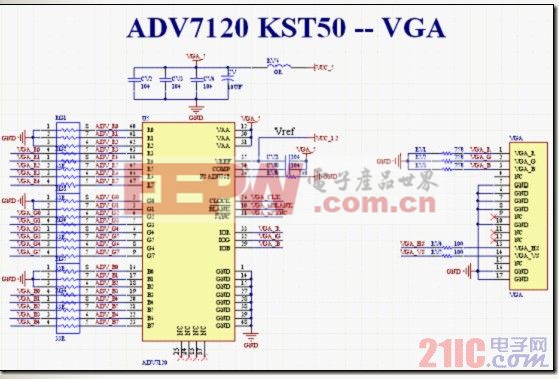

利用专用视频转换芯片,ADV7120等,将数字信号转换为VGA RGB的模拟信号。ADV7120为高速D/A芯片,将数字信号转换为模拟信号输给VGA,电路如下:

Bingo玩VGA也算是比较早了,当年也是视觉的诱惑,以及唯FPGA独尊的优势。于是之后一发而不可收拾。本章Bingo将自己这些年最终优化的VGA驱动模块,发布至此。本模块所有代码均Bingo独家创造,请尊重版权哈。

本设计已经封装成模块,只要修改时序参数、扫描时钟参数以及在vga_display.v中添加显示电路,即可。方便移植,希望对大家有用。

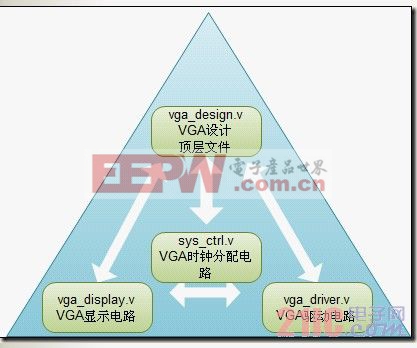

1、模块划分

(1)vga_design.v

工程顶层文件,例化各个模块。

(2)sys_ctrl.v

PLL时钟分配电路。

(3)vga_display.v

显示电路,根据时序,用于描述VGA的显示电路。

(4)vga_driver.v

VGA驱动电路,对时序,状态的约束。

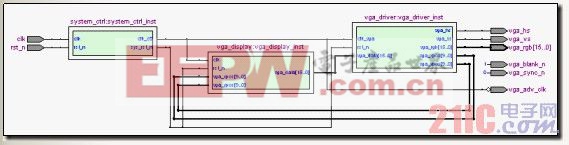

RTL图如下所示:

2、代码设计

Bingo例程以16bit RGB VGA驱动为例,不同位数的显示只要改一下vga_data即可。

前文以及代码讲述了那么多,此处不再贴完整代码,而是对代码中部分结构进行解析。

代码下载地址:http://blog.chinaaet.com/detail/21606.html

(1)vga_driver.v代码分析

a) 参数例化列表

#(

// VGA_1024_768_60fps_65MHz

// Horizontal Parameter ( Pixel )

parameter H_DISP = 11'd1024,

parameter H_FRONT = 11'd24,

parameter H_SYNC = 11'd136,

parameter H_BACK = 11'd160,

parameter H_TOTAL = 11'd1344,

// Virtical Parameter ( Line )

parameter V_DISP = 10'd768,

parameter V_FRONT = 10'd3,

parameter V_SYNC = 10'd6,

parameter V_BACK = 10'd29,

parameter V_TOTAL = 10'd806

)

这样写的目的是为了软件封装性,能够在例化的时候修改法分辨率,同时电路结构保持不变。

DISP,FRONT ,SYNC,BACK,TOTAL分别为显示期,消隐前肩,消音期,消隐后肩,总时间,各自对应各自的行场信号。

b) 行同步信号设计

//------------------------------------------

// 行同步信号发生器

reg [10:0] hcnt;

always @ (posedge clk_vga or negedge rst_n)

begin

if (!rst_n)

hcnt = 0;

else

begin

if (hcnt H_TOTAL-1'b1)

hcnt = hcnt + 1'b1;

else

hcnt = 0;

end

end

//------------------------------------------

always@(posedge clk_vga or negedge rst_n)

begin

if(!rst_n)

vga_hs = 1;

else

begin

if( (hcnt >= H_DISP+H_FRONT-1'b1) (hcnt H_DISP+H_FRONT+H_SYNC-1'b1) )

vga_hs = 0;

else

vga_hs = 1;

end

end

如上所示,分析代码可以知道,行同步信号的计数状态机按照时序的划分,是以下过程:H_DISP,H_FRONT,H_SYNC,H_BACK,这似乎和上述分析的VGA时序不是完全吻合。但是VGA时序是一个循环,顺推H_BACK个时终域便可以得到以上时期划分,但是这样更方便后续坐标计数,因为Bingo此处这样设计,当然实际证明是完全可行的。

注意:(hcnt >= H_DISP+H_FRONT-1'b1) (hcnt H_DISP+H_FRONT+H_SYNC-1'b1) 只是因为后续坐标计算,就把时序提前了1个时钟已达到同步。

评论