基于FPGA实现固定倍率的图像缩放

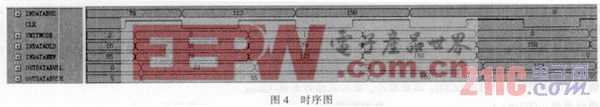

基于FPGA实现的仿真时序图如图4所示。本文引用地址:https://www.eepw.com.cn/article/190182.htm

在本例中时钟为输入的点时钟,为了在X3像素周期时输出2个像素:Y2和Y3,采用了扩充数据总线的方式。

2.2.2 基于FPGA实现列方向的卷积

数据流在行方向放大后写入双口RAM,然后从另一侧端口读出进行列方向的放大。由于行方向的卷积算法,双口RAM中至少应存储连续的3行输入图像像素数据,其中2行输入图像像素数据处于被读出状态,产生放大后的输出图像像素,另一行空间被写入当前的输入图像像素数据,循环刷新。

列方向的单元体和行方向相同,也由3个输入像素和4个输出像素组成,每种状态下也是同样的卷积系数,只是图像横向的空间变换成图像竖向的空间,因此基于FPGA实现列方向的卷积的方法与基于FPGA实现行方向的卷积的方法相同,此处不再赘述。

3 结束语

基于FPGA实现图像缩放,需要根据图像缩放的倍率确定包含适当数量像素的单元体。在单元体内部,根据图像缩放算法确定每个输出像素的计算公式和卷积系数,确定实现点时钟倍频效果的硬件方案。顺向映射方式输入和输出处于帧同步状态,由于输出像素数量多于输入像素,输出像素的点时钟频率要高于输入像素。本文行方向的放大过程,点时钟频率平均增加1/3倍,列方向的放大过程,点时钟频率还要继续增加1/3倍。实现倍频效果可以采用更高频的独立时钟,或者倍频输入点时钟,再或者增加数据总线宽度。为节省数据存储空间,当对图像放大时,先进行列方向的放大,后进行行方向的放大;当对图像缩小时,先进行行方向的缩小,后进行列方向的缩小。

基于FPGA实现图像缩放功能实时性强、分瓣率高。许多航空电子嵌入式图像处理系统是由固定的视频源和显示设备组成,系统中图像缩放的倍率是固定的。本文基于FPGA硬件实现固定倍率的图像缩放,能够大幅度降低设计难度,减少工作量。

基于FPGA硬件实现固定倍率的图像缩放的方法已经应用于某款航空电子产品中,电路板的原有硬件没有变动,对电路板中FPGA重新进行了设计,增加了新的内容,应用效果良好。

评论