2.2.1 基于FPGA实现行方向的卷积

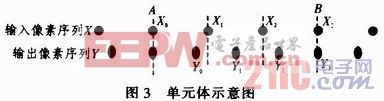

图像在行方向的放大比例为3:4,即单元体为3个输入像素和4个输出像素,如图3所示。本文引用地址:https://www.eepw.com.cn/article/190182.htm

输入图像的AB空间中均匀分布X1、X2、X3,3个像素,放大后输出图像的这个空间将输出y0、y1、y2、y3,4个像素。这个单元体的时序关系是:当输入X1像素时,输出Y0像素;当输入X2像素时,输出Y1像素;当输入X3像素时,输出Y2和Y3像素。行方向的卷积公式为:

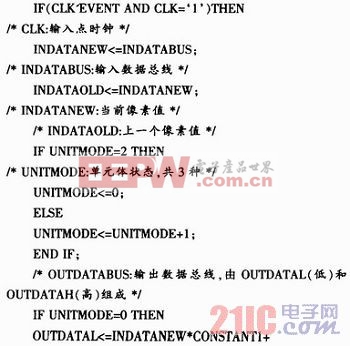

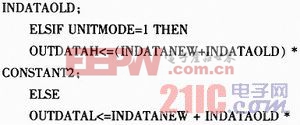

基于FPGA实现的源程序如下:

评论