基于FPGA和FLASH ROM的图像信号发生器设计

2 系统实现

2.1 USB接口模块

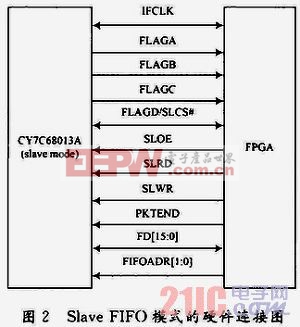

USB接口具有传输速度快、即插即用等优点,所以使用USB来实现PC机与系统的通信。CY7C68013A作为USB 2.0控制器,有3种接口工作模式:Ports,Slave FIFO和GPIF。根据系统构成和实际要求,选用Slave FIFO模式的数据传输方案。具体的硬件连接如图2所示。本文引用地址:https://www.eepw.com.cn/article/190175.htm

CY7C68013A通过固件编程来配置具体的功能。应用程序通过USB驱动程序建立与USB外部设备的联系。本文采用了Cypress公司提供的通用驱动CyUsb.sys,该驱动程序完全满足本系统设计的要求。应用程序可以通过两种方式来访问CyUsb.sys:

(1)使用Windows API如SetupDiXxxx和Deviceio Control;

(2)使用Cypress公司提供的CyAPI.lib。

本文采用CyAPI.lib来访问USB驱动,CyAPI.lib提供了简单高效的与Cyusb.sys通信的方法,方便掌握、可有效缩短USB设备的开发周期。

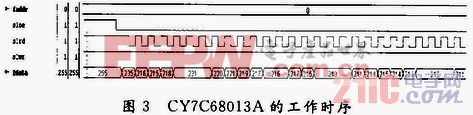

在完成图像数据写入功能时,FPGA接收到图像数据写入的命令后,使faddr地址指向用于下传数据的端点FIFO,然后开始获取来自USB控制器的数据,FPGA内部USB通信模块工作情况如图3所示。IFCLK是由FPGA提供的40MHz时钟,CY7C68013A的端点FIFO被配置为同步工作。

评论