基于TMS320F2812的最小系统设计

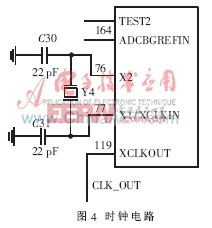

1.3时钟电路

锁向环(PLL)模块主要用来控制DSP 内核的工作频率,外部提供一个参考时钟输入,经过PLL倍频或分频后提供给DSP 内核。本系统采用基于PLL的晶体工作模式,通过外部无源晶体为芯片提供时钟基准,本文所选用的外部晶振是30 MHz。具体电路如图4所示。本文引用地址:https://www.eepw.com.cn/article/180693.htm

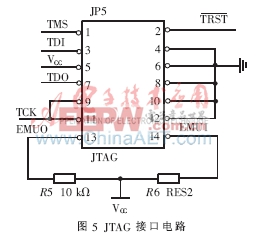

1.4 JTAG接口电路

JTAG接口提供对DSP内部Flash的烧写和仿真调试,它所具备的这些能力需要软件的配合,具体实现功能则由具体的软件决定。JTAG接口是一个业界标准,这部分的引脚定义不要随意改变。本设计中将其设计成一个标准的14针插座,可以供仿真器调试目标板。具体的连接如图5所示。

1.5外部接口电路

为了方便扩展及二次开发,将TMS320F2812的4个方向的各个主要引脚全部引出。采用4个30针的双排针脚式接口将120个重要的引脚引出,可以分配给地址线、数据线、AD模块和时钟电源等。在这里,具体的引脚外接就不再详述了,只介绍几个常用的外扩模块电路。当然,在对最小系统的利用时,可以增加相应的模块来完成特定的功能,例如可以增加RS-485通信电路,在扩展的同时要注意用DC-DC进行物理隔离,尤其在工业应用场合。

1.5.1 外扩RAM电路和外扩Flash电路

为了增加系统的程序存储空间,提高系统的工作效率,根据设计要求外扩了Flash电路和RAM电路。选用的RAM 型号为IS61LV25616AL,256 KB×16 bit大小。这里用了A0~A17共18根地址线,最大为256 KB;D0~D15 共16 根数据线。片选CS6和读写WR、RD 信号都由DSP引出。外扩的Flash型号为SST39VF800,512 KB×16 bit,方便用户烧写较大程序。本文比SRAM多了1根地址线,所以最大可以达到512 KB,片选信号用CS2。具体连接如图6所示。

评论